# Active-Matrix Field Emission Display with Amorphous Silicon Thin-Film Transistors and Mo-Tip Field Emitter Arrays

Yoon-Ho Song, Chi-Sun Hwang, Young-Rae Cho, Bong-Chul Kim, Seong-Deok Ahn, Choong-Heui Chung, Do-Hyung Kim, Hyun-Seok Uhm, Jin-Ho Lee, and Kyoung-Ik Cho

We present, for the first time, a prototype active-matrix field emission display (AMFED) in which an amorphous silicon thin-film transistor (a-Si TFT) and a molybdenumtip field emitter array (Mo-tip FEA) were monolithically integrated on a glass substrate for a novel active-matrix cathode (AMC) plate. The fabricated AMFED showed good display images with a low-voltage scan and data signals irrespective of a high voltage for field emissions. We introduced a light shield layer of metal into our AMC to reduce the photo leakage and back channel currents of the a-Si TFT. We designed the light shield to act as a focusing grid to focus emitted electron beams from the AMC onto the corresponding anode pixel. The thin film depositions in the a-Si TFTs were performed at a high temperature of above 360 °C to guarantee the vacuum packaging of the AMC and anode plates. We also developed a novel wet etching process for n<sup>†</sup>-doped a-Si etching with high etch selectivity to intrinsic aSi and used it in the fabrication of an inverted stagger TFT with a very thin active layer. The developed aSi TFTs performed well enough to be used as control devices for AMCs. The gate bias of the a-Si TFTs well controlled the field emission currents of the AMC plates. The AMFED with these AMC plates showed lowvoltage matrix addressing, good stability and reliability of field emission, and good light emissions from the anode plate with phosphors.

#### I. INTRODUCTION

The field emission display (FED) has emerged as a leading contender in display technologies because it combines the best features of the cathode ray tube (CRT) and flat panels [1], [2]. Whereas in a CRT the filament emits hot electrons, in an FED the field emitter array (FEA) cathode emits cold electrons to bombard phosphors in the anode plate. The matrix addressing of FEAs is mainly a passive multiplexing in conventional FEDs, in which the driving voltage is high except for the specially processed small gate FEA by Candescent [3]. The emission currents of passive multiplexed FEAs are very sensitive to driving voltage, and this causes a problem in uniformity. While much effort has been focused on simple-matrix FEA cathodes, stability and reliability of the conventional FEA cathodes are still key problems in the commercialization of FEDs. These difficulties can be overcome by applying an active-matrix cathode (AMC) scheme [4]-[9]. The AMC has many advantages, such as low-voltage addressing regardless of the high voltage required for field emission, good pixel isolation that reduces cross-talk and fatal short failure, and good field emission uniformity and stability.

Metal-oxide-semiconductor field-effect transistor (MOSFET)-controlled Si FEAs [4], [5] and polycrystalline silicon (poly-Si) [6]-[8] and amorphous silicon (a-Si)-based FEAs [9] controlled by thin-film transistors (TFTs) have been employed in AMC architecture. However, a fully vacuum-packaged active-matrix field emission display (AMFED) with an AMC plate on glass has not been reported. The control transistor for the AMC has been MOSFET or TFT according to the substrate. The glass substrate is indispensable to the fabrication of low-price, large-

Manuscript received Nov. 21, 2001; revised May 9, 2002.

This work was financially supported by the Korea Ministry of Information and Communication.

Yoon-Ho Song (phone: +82 42 860 5295, e-mail: yhsong@etri.re.kr), Chi-Sun Hwang (e-mail: hwang-cs@etri.re.kr), Bong-Chul Kim (e-mail: kimbong@etri.re.kr), Seong-Deok Ahn (e-mail: lovesky@etri.re.kr) Choong-Heui Chung (e-mail: choong@etri.re.kr), Jn-Ho Lee (e-mail: leejinho@etri.re.kr), and Kyoung-Ik Cho (e-mail: kicho@etri.re.kr) are with Basic Research Laboratory, ETRI, Daejeon, Korea.

Young Rae Cho (e-mail: yescho@pusan.ac.kt) is with the Division of Materials Science and Engineering, Pusan National University, Busan, Korea.

Do-Hyung Kim(e-mail: phydhkim@ams1.knu.ac.kr) is with the Department of Physics, Kyungpook National University, Daegu, Korea.

Hyun-Seok Uhm(e-mail: hsuhm@pkl.co.kr)iswithPKLCo.Ltd.,Cheonan,Chungnam,Korea.

area displays. Thus, the successful implementation of an a-Si TFT in the AMC is a crucial point for the development of the FED as a competitive display device. In our study, a prototype AMFED with the AMC on a glass substrate was fabricated for the first time and demonstrated to show good display images with a low-voltage scan and data driver circuits. We designed and developed a new cathode architecture with a light shield and focusing grid including a novel a-Si TFT process for AMC plates.

# II. DEVICE AND PROCESS DESIGN FOR THE AMFED

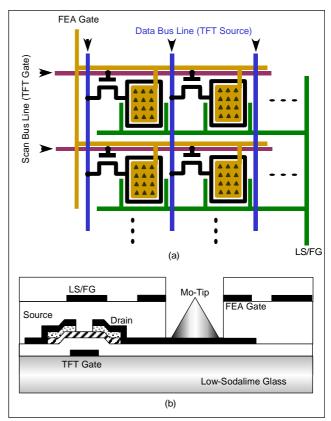

The prototype AMFED panel consisted of an AMC plate and an anode plate of green phosphor having 64×(64×3) subpixels with a pitch of 450 µm by 200 µm. Figure 1 shows schematic diagrams of the AMC plate and its sub-pixel structures with display input signals. We designed the AMC sub-pixel to have an a-Si TFT as a control switch for the Motip FEAs on a low-sodalime glass. In each sub-pixel, the conical Mo-tips were constructed on the drain electrode of an a-Si TFT together with a light shield (LS)/focusing grid (FG) that is described in detail below. We selected low-sodalime glass as the AMC substrate for its feasibility in the a-Si TFT process and its immunity to alkali metals. The immunity can be obtained with the help of a proper buffer layer deposited on the substrate. The low-sodalime glass also has a relatively large thermal expansion coefficient, which is necessary for frit sealing in vacuum packaging, and good vacuum durability, which is indispensable in the fabrication of FEDs. We designed the a-Si TFTs in the conventional inverted stagger structure that has been commonly used in TFT-switched liquid crystal displays (LCD) [10]. A slight modification in the a-Si TFTs from the conventional device and process architecture enabled us to fabricate a large-area AMFED for a relatively low cost.

Without further modification, the a-Si active layer in our AMC would be exposed to stray light from the front anode plate which contains phosphors, causing light-induced leakage currents and consequent deterioration of the switching properties of the a-Si TFT. Therefore, it was necessary to add a light shield on the backside of the gate electrode of our AMC; this differed from the TFT-LCD in which the gate electrode blocks the light from a back lighting unit. To remove the light-induced leakage currents, we designed our AMC to have a light shield of metal above the a-Si TFT. The light shield did not require any additional process because it could be formed through an appropriate layout with the electron extraction gate of the Mo-tip FEA. Under the normal operation of the AMC, the light shield is biased to zero or a negative volt to get rid of

Fig. 1. Schematic diagrams of the AMC plate with display signal inputs and a cross-section of an AMC sub-pixel with an a-Si TFT and a Mo-tip FEA.

the back channel leakage currents of the a-Si TFT induced by the FEA-gate bias voltage. We intended the light shield to act as a focusing grid to focus emitted electron beams from the AMC onto the corresponding anode pixel by drawing the LS around the Mo-tip FEA as well as above the a-Si TFT.

The process design of the AMC on the glass substrate was straightforward: an a-Si TFT process followed by Mo-tip FEA formation on the drain electrode of the a-Si TFT. However, we had to consider the deposition temperature of the a-Si films from the viewpoint of the vacuum packaging process in the FED. During the vacuum sealing process, the temperature of the samples rises above the melting temperature of frit glass, around 350 °C. This high temperature process can bring about serious degradation to the electrical characteristics of an a-Si TFT fabricated by the conventional plasma-enhanced chemical vapor deposition (PECVD) process [10]. Therefore, the deposition temperature of thin films in an a-Si TFT must be high enough to prevent the samples from being damaged by the high-temperature vacuum sealing process. In our fabrication process of the AMC we kept the deposition temperature of the a-Si films above 350 °C. We also lowered the vacuum sealing temperature to below 350 °C by using an in-line laser-assisted packaging process, which resulted in successful maintenance of the a-Si TFT performance, even after the vacuum packaging.

# III. FABRICATION PROCEDURE OF THE AMFED

The a-Si TFT process in our AMC plate followed the conventional inverted stagger structure procedure. However, to achieve a very thin active layer of below 600 minimize the number of process steps, we developed a new wet back-channel-etch (BCE) process using CH<sub>3</sub>COOH, HNO<sub>3</sub>, and HF solutions for the n<sup>+</sup>-doped a-Si etching. The buffer layer of amorphous silicon nitride (a-SiN<sub>x</sub>) was deposited by PECVD at 260 °C onto cleaned glass substrates. A 100-nm-thick Cr was sputtered and patterned to form the TFT gate and scan bus line. Then the gate a-SiN<sub>x</sub>, intrinsic a-Si, and n<sup>+</sup>-doped a-Si were successively deposited by PECVD at 380 °C without breaking the vacuum. The film thickness of the SiNx, intrinsic a-Si, and n<sup>+</sup>-doped a-Si was 350 nm, 60 nm, and 40 nm, respectively. A 150-nm-thick Cr film was sputtered on the n<sup>+</sup>-doped a-Si layer and etched to form the source/drain and data bus line. We then used the wet BCE process to remove the n<sup>+</sup>-doped a-Si layer on the active channel of the a-Si TFT. The developed wet BCE technique showed a high etch selectivity of up to 15:1 between the n<sup>+</sup>-doped a-Si and intrinsic a-Si while the selectivity mainly varied with the HF-volume ratio of stock solutions. The etch rate of the n<sup>+</sup>-doped a-Si was easily controlled by changing the HF-volume ratio from 10 nm/min to 180 nm/min with a very high uniformity of within 5% in a 5-inch wafer. These etch properties enabled us to fabricate the BCE-processed a-Si TFT with a very thin active layer.

After the BCE process, an 800-nm-thick a-SiNx and a 200nm-thick Cr were deposited on the sample for the FEA gate dielectric and FEA gate, respectively. The FEA gate was patterned by wet etching of the Cr film, and then a 120-nmthick buffer a-SiN<sub>x</sub> was deposited by PECVD to prevent the peeling-off of the FEA gate and/or dielectric film from the sample during the post-evaporation process for the Mo-tips. FEA gate holes of about 1.1 µm in diameter were formed on the drain electrode of the a-Si TFT through lithography using a contact aligner and dry etching of the Cr and a-SiNx films. Al for the parting layer and Mo for the tips were evaporated onto the sample with an appropriate angle to the e-beam sources. Finally, the Mo film was lifted off by a KOH dip and conical Mo-tips remained inside the FEA gate holes. The overall tipformation process in the AMC fabrication was optimized for elimination of the side effects on the a-Si TFTs.

For the anode plate, the green phosphor of ZnS:Cu,Al was printed using lithography on an ITO-patterned glass substrate. Several bar-type spacers made of photosensitized glass were

placed on the anode plate. The height and width of the spacers were 450  $\mu m$  and 100  $\mu m$ , respectively. The anode plate was annealed at 430 °C in an air-ambient oven before vacuum packaging. The in-line vacuum packaging of the AMC and anode plates, including the activation process of a non-evaporable getter, was performed in a load-locked high vacuum chamber system using a continuous Nd:YAG laser. The AMC plate was kept at a temperature as low as about 300 °C during the vacuum packaging. The detailed vacuum sealing and getter activation processes were described in recent reports [11], [12].

### IV. RESULTS AND DISCUSSION

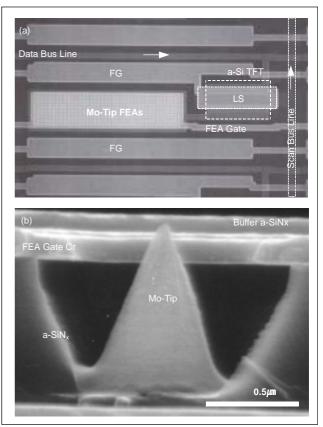

We successfully integrated a-Si TFTs with Mo-tip FEAs on a glass substrate for an AMC plate. Figure 2 shows scanning electron microscopy (SEM) images for the top view of the fabricated AMC sub-pixel and the cross-sectional view of a single Mo-tip in the FEA gate hole. The AMC sub-pixel had an a-Si TFT with an LS above it, a Mo-tip array having 400 Mo-tips, and two FGs along with the FEA gate and scan/data bus lines, in which the LS was connected with one of the two

Fig. 2. SEM images for the top view of a fabricated AMC and a cross-sectional view of a single Mo-tip in the FEA gate hole.

FGs, and the scan and data bus lines terminated at the gate and source of the a-Si TFT, respectively. The Mo-tips inside the FEA gate holes had an end-radius of about 500  $\,$  and a height of 1.0  $\mu m$ . The gate length was 20  $\mu m$  and the channel width was 100  $\mu m$  for the a-Si TFT.

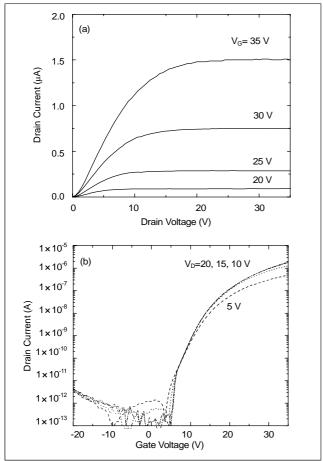

The output and transfer characteristics of the wet BCE-processed a-Si TFT with a 60-nm-thick active a-Si layer deposited at 380 °C are shown in Fig. 3. The field effect mobility and threshold voltage extracted from the saturation region of the a-Si TFT were approximately  $0.15~\rm cm^2/V \cdot s$  and  $9.5~\rm V$ , respectively. The a-Si TFT processed at such a high temperature of 380 °C showed moderately degraded properties compared to that processed at around 300 °C with values of  $0.7~\rm cm^2/V \cdot s$  and  $4.5~\rm V$ . However, the wet BCE and high-temperature processed a-Si TFT showed good linear and saturation behavior with a relatively high drive current of several  $\mu A$  (Fig. 3(b)). The devices showed little change for many hours in the transfer and output characteristics with electrical stress in the on-state biasing. These results indicate

that the developed a-Si TFT can be efficiently used as a switching device for an AMC considering the required currents of about  $1-10 \,\mu\text{A}$  per sub-pixel in FED applications.

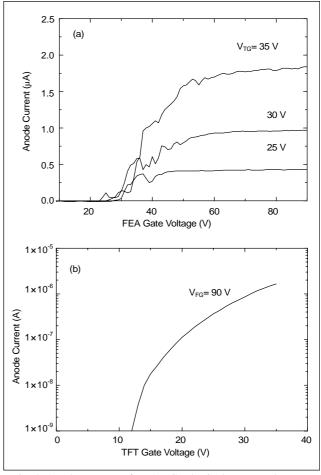

Figure 4 exhibits the field emission characteristics of the fabricated AMC sub-pixel as functions of FEA ( $V_{FG}$ ) and TFT gate voltages ( $V_{TG}$ ). The field emission measurements were done under a vacuum of about  $1\times10^6$  Torr at room temperature and the data were plotted after an appropriate aging process for the Mo-tip FEA. The anode voltage was kept at 450 V with an AMC-to-anode spacing of about 500  $\mu$ m during the measurements. The aging process at a relatively high emission current led to stable curves in the field emission plots. Moreover, the AMC device had very stable aging kinetics for field emitters with the limitation of emission currents by the a-Si TFT, and thus we could successfully activate Mo-tips to emit electrons without any tip-failure. Anode currents versus FEA gate voltage for various  $V_{TG}$  are shown in Fig. 4(a). At each  $V_{TG}$ , the anode currents were well saturated above about 55 V

Fig. 3. Output and transfer characteristics of the a-Si TFT with a gate length of 20  $\mu m$  and a channel width of 100  $\mu m$ . The  $V_G$  and  $V_D$  denote the TFT gate and drain bias voltages, respectively.

Fig. 4. Anode currents of an AMC sub-pixel at an anode voltage of 450 V: (a) as a function of the FEA gate voltage ( $V_{FG}$ ) at various TFT gate voltages ( $V_{TG}$ ), (b) as a function of the TFT gate voltage at a  $V_{FG}$  of 90 V.

for V<sub>FG</sub> due to the limitation in field emission currents by the a-Si TFT. The saturated anode current was nearly identical to the drain current of the a-Si TFT operated in the saturation region for a given TFT-gate bias voltage (Fig. 3(a)). Some fluctuations in the field emission currents of the AMC sub-pixels were below the saturation region, which was due to the linear operation of the a-Si TFT. The linear region operation of the a-Si TFT was subjected to the intrinsic fluctuations of the field emission, resulting in an unstable field emission even for an AMC device. Figure 4(b) shows the switching characteristics of the AMC sub-pixels by the TFT gate at a constant  $V_{\text{FG}}$  of 90 V. The off-state currents in Fig. 4(b) had some errors caused by the limitation of our measurement system at a low current level. We found that the field emission currents from the Mo-tip FEAs did nearly conform to the transfer characteristics of the a-Si TFT shown in Fig. 3(b). The TFT gate efficiently switched the anode currents for a constant V<sub>FG</sub>, showing a high on/off ratio of above 1000 times in emission-currents by sweeping the TFT gate bias within a 30 V range.

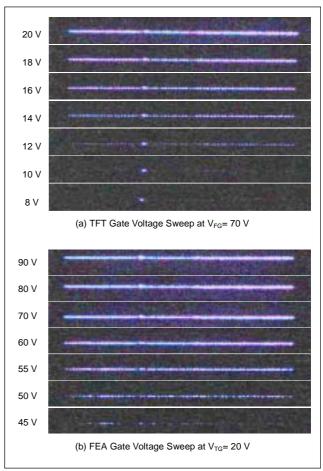

We investigated the line-by-line field emission properties of the AMC plate with an anode plate having a blue phosphor of CaS:Pb [13] in the vacuum chamber (Fig. 5). During the tests all TFT gate lines were connected to a common bias, and each source line was selected for line emission. The light emission started at 45 V-and saturated over a 60 V-FEA-gate bias voltage for the  $V_{TG}$  of 20 V. The light emission saturation for the increment of the FEA-gate bias confirmed the control of emission currents by the TFT-gate bias. Sweeping the TFT-gate bias voltage from 8 V to 20 V completely controlled the gray scale of light emissions.

We specially noted that the LS/FG was biased to zero volt during the measurements shown in Figs. 4 and 5. The LS/FG bias of 0 V resulted in the complete turn-off of field emission currents at a constant FEA-gate bias voltage. In case of the no LS/FG structure, the AMC sub-pixel was hardly turned-off by the TFT gate showing large leakage currents of above 10<sup>-8</sup> A. Furthermore, the leakage current was still large even for the floating bias to the LS/FG. This implies that the function of the LS/FG is to prohibit the back channel of a-Si TFT turning-on by the FEA-gate bias voltage and to block the lights from the anode phosphor plate into the a-Si TFT in the AMC, resulting in a high on/off ratio for field emission currents. With the introduction of the LS/FG in the AMC architecture, we can easily achieve a high contrast AMFED addressed by a lowvoltage scan and data signals through the a-Si TFT. In addition, the LS/FG biased zero or negative volt acts to focus electron beams from the cathode onto the corresponding anode pixel enhancing the color purity of the AMFED, as in the previous reports by Tang et al. [14], [15].

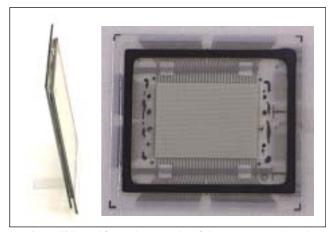

Figure 6 shows the first prototype AMFED panel vacuum-

Fig. 5. Line-by-line light emissions for the AMC plate at an anode voltage of 450 V: (a) as a function of the TFT gate voltage at a  $V_{\rm FG}$  of 70 V, (b) as a function of the FEA gate voltage at a  $V_{\rm TG}$  of 20 V.

Fig. 6. Side and front photographs of the vacuum-packaged AMFED panel.

packaged using the in-line laser-assisted sealing process. The final pressure inside the fabricated AMFED panel was estimated to be less than  $5\times10^{-6}$  Torr through an indirect

measurement method. It was done by comparing the pressure of an isolated high vacuum chamber before and after breaking the AMFED panel inside the chamber. Unlike the conventional FED, the AMFED panel has no evacuation tube and thus the in-line laser-assisted packaging process gave us an ideal flat panel display.

On the other hand, the vacuum packaging process can give rise to thermal damage to the a-Si TFT, resulting in some fatal errors in controlling field emissions. We checked the stability of the a-Si TFT and controllability of field emission currents after the laser-assisted vacuum packaging process. Figure 7 shows the transfer characteristics of the a-Si TFT in the vacuum-sealed AMC plate for a V<sub>D</sub> of 5 V. We did not find any changes in the transfer characteristics of the a-Si TFT after the vacuum packaging process, which confirms the preservation of the a-Si TFT with the packaging process. The maximum temperature of the packaging process was around 380 °C at the frit-sealing site and around 300 °C in the environment. The maximum temperature of the TFT sites during the packaging process was measured with a thermocouple to be about 330 °C, which was much lower than the deposition temperature (380 °C) of the active a-Si layer in the TFT.

Fig. 7. Transfer characteristics of an a-Si TFT in the AMC plate before and after the vacuum packaging process.

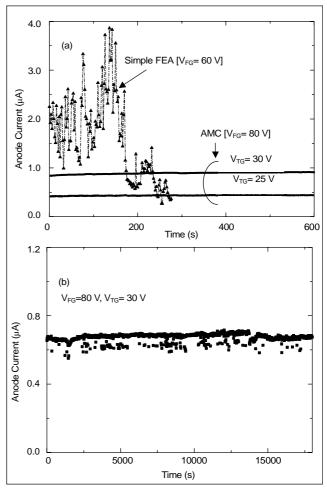

The stability and reliability of the AMC plate was tested through a continuous-mode operation of field emissions (Fig. 8). The data points in Fig. 8 were taken from the mean values of 5 anode currents measured for 1 second with constant voltages. Figure 8(a) exhibits the field emission stability of the AMC devices compared to simple FEAs. The AMC showed very stable emission currents without any degradation, while the simple FEAs showed a large fluctuation in emission currents. This result suggests that field emission can be strongly

Fig. 8. Anode currents as a function of time at an anode voltage of 450 V showing (a) stability of a simple FEA and an AMC sub-pixel in a short time, and (b) reliability of an AMC sub-pixel in a relatively long time.

stabilized by an a-Si TFT in an AMC plate. The anode current of the AMC sub-pixel was maintained at the same level of over 18000 s, whereas some fluctuation deviating from the main trend of the emission current was observed. We think that the fluctuation was caused by a noisy interface between the PC and measuring units. We also confirmed that the emission currents were maintained through two days in the continuous-mode operation. In general, the FEA cathode operates in the pulse mode with a duty ratio of below 1/10, so we can say that there was no degradation for more than a 20-day pulse-mode operation. We think that there is no problem concerning reliability in integration of an a-Si TFT with a Mo-tip FEA.

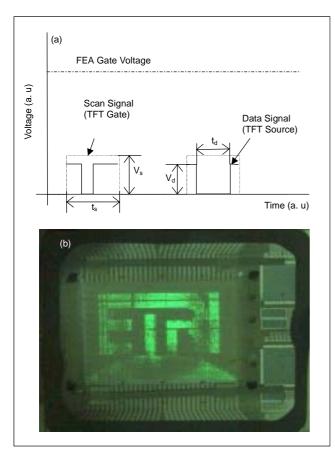

Figure 9 shows a schematic signal diagram of the driving method for the fabricated AMFED panel and a displayed image on the panel. The display signals from the scan and data drivers were addressed to the gate and source of the a-Si TFT, respectively, in each sub-pixel. If the scan pulse had an amplitude of  $V_{\rm s}$  and a width of  $t_{\rm s}$  and the data pulse had  $V_{\rm d}$  and

Fig. 9. Schematic signal diagram for scan and data signals with a constant FEA gate voltage and a displayed image (ETRI Logo) on the AMFED panel with a 30 V scan and data pulses.

$t_{\text{d}}$ , then the electrons were emitted under the condition of ( $V_{\text{s}}$ - $V_d$ ) >  $V_T$ , where  $V_T$  is the threshold voltage of the a-Si TFT. As a result, the scan and data signals can be lowered irrespective of a constant high voltage for field emissions, so the power consumption in driving the AMFED and the cost for integrated driver circuits can be greatly reduced. In addition, the electron emission was maintained only for t<sub>d</sub> within a given t<sub>s</sub> determined by the number of scan lines and display refresh rate. Therefore, the gray scale can be easily obtained by pulse widthmodulated data signals addressed to the source of the a-Si TFT in the AMC sub-pixel. We achieved good images from the prototype AMFED with scan and data signals having a pulse amplitude of 30 V while the FEA gate and the anode plate kept constant voltages of 70 V and 400 V, respectively. Some defective points in the image shown in Fig. 9(b) were due to Mo-tip failures during the fabrication process. The fabricated AMFED successfully demonstrated good display images with a relatively high contrast ratio using low-voltage scan and data driver circuits, suggesting a technological breakthrough in FEDs.

## V. CONCLUSION

Our investigation confirmed the feasibility of AMFED technology through integration of a-Si TFTs with Mo-tip FEAs on a glass substrate. The field emission properties of the fabricated AMCs were well controlled by the TFT gate bias, showing good stability and reliability of field emissions and the possibility of low-voltage matrix addressing regardless of a high voltage for the field emission. The LS/FG in the AMC architecture gave a complete turn-off of field emission currents at a constant voltage required for field emission. In addition, the new wet BCE process and high temperature deposition of the a-Si film allowed us to fabricate inverted stagger TFTs with an ultra thin active layer and to guarantee the vacuum packaging of the AMC and anode plates using the in-line laserassisted sealing process. The fabricated AMFED successfully demonstrated good display images with a low-voltage scan and data signals addressed to the a-Si TFT. The developed AMC technology with an in-line laser-assisted vacuum packaging process is very promising for highly stable, low-voltage driven FED applications.

#### **ACKNOWLEDGEMENTS**

The authors would like to thank Dr. Yun and Dr. Park for the anode preparation of CaS:Pb phosphor, and Mr. Cha, Mr. Song, and Mr. Kim in SAIT for the vacuum packaging and driving of the AMFED panel.

#### REFERENCES

- [1] S.J. Newman, R.T. Smith, and C. Penn, "Development of a 5.1-in. Field-Emission Display," *Tech. Digest of Society for Information Display Symposium*, 1998, pp. 95-97.

- [2] C.J. Curtin and Y. Iguchi, "Scaling of FED Display Technology to Large Area Displays," *Tech. Digest of Society for Information Display Symposium*, 2000, pp. 1263-1265.

- [3] C.J. Spindt, T. Fahlen, J.M. Macaulay, C.J. Curtin, and R.M. Duboc, "ThinCRT<sup>TM</sup> Flat-Panel-Display Construction and Operating Characteristics," *Tech. Digest of Society for Information Display Symposium*, 1988, pp. 99-102.

- [4] J. Itoh, "A New Actively Controllable Si FEA for FED Application," Proc. of 3th Int'l Display Workshops, 1996, pp. 155-158.

- [5] D. Kim, S.J. Kwon, and J.D. Lee, "New Cathode Structures of Si-Based Field Emitter Arrays," Proc. of 9th Int'l Vacuum Microelectronics Conf., 1996, pp. 534-537.

- [6] G. Hashiguchi, H. Mimura, and H. Fujita, "A Novel Multi-Layered Device of Polycrystalline Silicon Field Emitters and Thin Film Transistor for Field Emission Displays," *Proc. of 3th Int'l Display Workshops*, 1996, pp. 159-162.

- [7] Y.-H. Song, J.H. Lee, S.-Y. Kang, J.-M. Park, and K.I. Cho,

- "Monolithic Integration of Polycrystalline Silicon Field Emitter Array and Thin-Film Transistor for Active-Matrix FEDs," *Tech. Digest of Society for Information Display Symposium*, 1998, pp. 189-192.

- [8] Y.-H. Song, J.H. Lee, S.-Y. Kang, S.-Y. Choi, K.-S. Suh, M.-Y. Park, and K.I. Cho, "A Prototype Active-Matrix Field Emission Display with Poly-Si Field Emitter Arrays and Thin-Film Transistors," J. Korean Vacuum Science & Technol., vol. 3, 1999, pp. 33-37.

- [9] H. Gamo, S. Kanemaru and J. Itoh, "A Field Emitter Array Monolithically Integrated with a Thin Film Transistor on Glass for Display Applications," *Applied Surface Science*, vol. 146, 1999, pp. 187-192.

- [10] R.A. Street, Hydrogenated Amorphous Silicon, Cambridge University Press, Cambridge, 1991.

- [11] B.G. Song, S.N. Cha, N.S. Park, N.S. Lee, J.M. Kim, J.S. Shin, C.H. Lee, C.O. Kim, and J.P. Hong, "Development of in-situ Laser Vacuum Annealing and Sealing Processes for an Application to Field Emission Displays," *Proc. of 14th Int'l* Vacuum Microelectronics Conf., 2001, pp. 219-220.

- [12] S.N. Cha, J.Y. Choung, B.G Song, J.M. Choi, I.T. Han, N.S. Park, J.E. Jung, N.S. Lee, and J.M. Kim, "Improved Performance of Nonevaporable Getter Activated by a Continuous Wave Infrared Laser," *J. Vac. Sci. Technol.*, vol. B19, 2001, pp. 870-873.

- [13] S.J. Yun, Y.S. Kim, and S.-H. K. Park, "Fabrication of CaS:Pb Blue Phosphor by Incorporating Dimeric Pb<sup>2+</sup> Luminescent Centers," *Applied Physics Lett.*, vol. 78, 2001, pp. 721-723.

- [14] C.-M. Tang, T.A. Swyden, and A.C. Ting, "Planar Lenses for Field-Emitter Arrays," J. Vac. Sci. Technol., vol. B13, 1995, pp. 571-575.

- [15] C.-M. Tang, T.A. Swyden, K.A. Thomason, L.N. Yadon, D. Temple, C.A. Ball, W.D. Palmer, J.E. Mancusi, D. Vellenga, and GE. McGuire, "Emission Measurements and Simulation of Silicon Filed-Emitter Array with Linear Planar Lenses," *J. Vac. Sci. Technol.*, vol. B14, 1996, pp. 3455-3459.

Yoon-Ho Song received the BS degree in physics from Kyungpook National University in 1986, and the MS and PhD degrees in physics from Korea Advanced Institute of Science and Technology in 1988 and 1991. Since he joined ETRI in 1991, he has been involved in flat panel display research such as

active-matrix liquid crystal displays and active-controlled field emission displays using polycrystalline or amorphous silicon thin-film transistors. His research interests include disordered semiconductor and field emission physics and their applications including flat panel display technologies.

Chi-Sun Hwang was born in Daejon, Korea, in 1969. He received the BS degree in physics from Seoul National University, in 1991. He received the MS and PhD degrees in physics from Korea Advanced Institute of Science and Technology in 1993 and 1996, respectively. From 1996 to 2000 he worked as a Senior

Technical Staff in the Hyundai Electronics. Since 2000 he has been with ETRI as a Senior Engineer. His current research interests include field emission displays and thin-film transistors.

Young-Rae Cho received his BS degree from Pusan National University in 1984 and MS from KAIST, Korea in 1986. He received the PhD degree from Stuttgart University, Germany, in 1994. From 1999 to 2002 he was engaged in the development of field emission displays in ETRI as a Senior Engineer. He is currently

working as Assistant Professor in Pusan National University, Busan, Korea.

**Bong-Chul Kim** received the MS and PhD degrees in inorganic material engineering from Kyungpook National University, in 1997 and 2002, respectively. From 1989 to 2000 he worked as a Senior Technical Staff in Orion Electric Co. Ltd. From 2000 to 2001 he was engaged in the development of TFT-LCD in

LGPhilips LCD Ltd. Since 2001 he has been with ETRI as a Senior Engineer. His current research interests include field emission displays and carbon nanotubes.

Seong-Deok Ahn was born in 1968 and received the BS degree in materials science & engineering from Han Yang University in 1991 and the MS and PhD degrees from KAIST in 1994 and 2000, respectively. He joined ETRI in 2000 and has been engaged in the research and development of display devices and nano-

devices such as digital (or electronic) paper, field emission displays, and carbon nanotubes.

Choong-Heui Chung received the BS and MS degrees in materials science & engineering from Seoul National University, in 1997 and 1999, respectively. From 1999 to 2001, he was a member of Engineering Staff for Hyundai Electronics. Since he joined ETRI in May 2001, he has been mainly interested in research for the

process and characterization in active matrix field emission displays.

**Do-Hyung Kim** received the MS and PhD degrees in solid-state physics from Kyungpook National University. Since 1999, he has been engaged in research and development of active matrix field emission displays with a-Si TFT and field emitter arrays. He is currently interested in nanophysics and technology based

on carbon nanotubes.

Hyun-Seok Uhm was born in Seoul, Korea, in 1974. He received his BS and MS degrees in electrical engineering from Hanyang University in 1997 and 1999, respectively. Since 2000, he had been a Student Researcher in ETRI. He is currently working towards the PhD degree at the same university, studying active matrix field

emission displays and microwave amplifiers using field emission arrays.

Jin-Ho Lee received his MS degree in physics from Korea University, Korea, in 1982. In 1982, he joined ETRI. He has been engaged in the research and development of semiconductor devices and field emission displays. He received his PhD degree in physics from Kyungpook National University in 1998. From 1995, he was

a Principal Researcher and Information Display Team Leader in ETRI. His research field is FEDs, TFTs, SODs (system on display) and FPDs.

**Kyoung-Ik** Cho received the BS degree in materials science from Ulsan Institute of Technology in 1979, and the MS and PhD degrees in material science and engineering from Korea Advanced Institute off Science and Technology in 1981 and 1991, respectively. He joined ETRI in 1981. He has been working on

the development of advanced flat panel display devices, field emission display and digital paper, and next-generation memory devices, such as, ferroelectric memory, optical data storage devices, and corresponding driving power ICs. At present, he is the Director of the Wireless Communication Devices Department at ETRI-Basic Research Laboratory.