# Frequency-Dependent Line Capacitance and Conductance Calculations of On-Chip Interconnects on Silicon Substrate Using Fourier cosine Series Approach

H. Ymeri, B. Nauwelaers, S. Vandenberghe, K. Maex, D. De Roest and M. Stucchi

Abstract - In this paper a method for analysis and modelling of coplanar transmission interconnect lines that are placed on top of silicon-silicon oxide substrates is presented. The potential function is expressed by series expansions in terms of solutions of the Laplace equation for each homogeneous region of layered structure. The expansion coefficients of different series are related to each other and to potentials applied to the conductors via boundary conditions. In the plane of conductors, boundary conditions are satisfied at N<sub>d</sub> discrete points with N<sub>d</sub> being equal to the number of terms in the series expansions. The resulting system of inhomogeneous linear equations is solved by matrix inversion. No iterations are required. A discussion of the calculated line admittance parameters as functions of width of conductors, thickness of the layers, and frequency is given. The interconnect capacitance and conductance per unit length results are given and compared with those obtained using full wave solutions, and good agreement have been obtained in all the cases treated

Index Terms — Interconnects, Doplanar strip line, Fourier series approach, silicon substrate, point matching procedure.

### I. Introduction

The conducting substrates cause different effects, e.g. coupling effects. For low substrate conductivity (up tp 10 S/m), there are strong capacitive coupling effects between adjacent lines due to very small line-to-ground capacitances in comparison to line-to-line capacitances. In this case, the capacitive coupling dominates the overall coupling behaviour. Transmission interconnect lines on MIS structures have been investigated for many years. There are many techniques for computing the interconnect shunt admittance parameters. In [2], [3] Hasegawa et. al. presented an analysis of microstrip line on a Si-SiO<sub>2</sub> system using parallel-plate waveguide model. In [1], the new model is developed to represent fin line and wide line interconnect behaviour over a 20 GHz frequency range and includes the substrate conductance effects. In [4], propagation properties of multilayer coplanar lines on different types of silicon substrates are investigated. In [5,6], quasi-analytical analysis of broadband properties of multiconductor transmission lines on semiconducting substrates is done, and the calculated results for line parameters as function of frequency are discussed. Numerous electromagnetic approaches have been published which contains results of numerical full-wave or quasi-TEM analyses [7 - 12]. We can mention, the method based upon the classical mode-matching procedure [7], the spectral-domain analysis method [8, 9], and the finite element method [10] have been investigated for this structure. Recently quasi-TEM analysis on coplanar structure has made the incorporation of metallic conductor losses in the analysis possible and has provided a physical basis for the

Manuscript received September 11, 2001; revised November 6, 2001.

H. Ymeir, B. Nauwelaers, and S. Vandenberghe are with Kathoolieke Universiteit Leuven, Department of Electrical Engineering(ESAT, Div, ESAT-TEEMIC, Kasteelpark Arenberg 10, B-3001 Leuven-Heverlee, Belgium.

<sup>(</sup>e-mail: has an.ymeri@esat.kuleuven.ac.be)

K. Maex, D. De Roest, and M. Stucchi are with IMEC, Leuren, Belgium.

construction of equivalent circuits [11]. In [12], the CAD-oriented equivalent-circuit modeling procedure based on a quasi-stationary spectral domain approach which takes into account the skin effect in the silicon semiconducting substrate is presented.

The purpose of this paper is a slight modification of a recently proposed series expansion method [13 - 15], developed for the electrical modeling of lossy-coupled multilayer interconnection lines, that does not involve iterations and yields solutions of sufficient accuracy for most practical interconnections as used in common VLSI chips. We use here a Fourier series restricted to cosine functions. The solution for the layered medium is found by matching the potential expressions in the different homogeneous layers with the help of boundary conditions. In the plane of conductors, the boundary conditions are satisfied only at a finite, discrete set of points (point matching procedure) [16].

### II. METHOD OF ANALYSIS

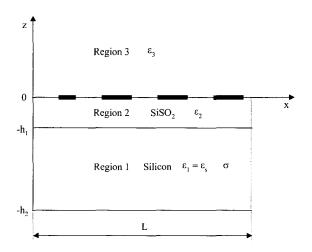

The new modeling procedure is described for typical on-chip interconnects on a lossy silicon substrate with permittivity  $\varepsilon_s$  and conductivity  $\sigma$ , as illustrated in Fig. 1. It consists of the signal lines and two ground lines in the same plane.

**Fig. 1.** Cross-sectioned view of the coplanar interconnect lines on lossy silicon substrate.

The whole structure in x direction is bounded by open surfaces (Neuman type boundary conditions) x = 0 and x = L, respectively.

If the conductivity is small enough or the frequency is high enough but still well below the quasi-stationary frequency limit, in each layer of the structure, the electric potential must be a solution of the Laplace equation

$$\frac{\partial^2 \varphi}{\partial z^2} + \frac{\partial^2 \varphi}{\partial x^2} = 0. \tag{1}$$

In the most general case, the field variation in the x direction could be described as a Fourier integral. However, for numerical computations, discrete series are easier to handle than integrals. For this reason, we use an expansion of the potential function in terms of cosine functions [13-15]. The functions  $\cos[m(\pi/L)x]$  form a complete orthogonal set [17] over the domain 0 < x < L for the integer values of m.

Thus, we may express the potential function  $\phi$  in regions 3 and 2 as follows :

$$\varphi_3(x,z) = a_0 + \sum_{m=1}^{\infty} a_m e^{-(m\pi/L)z} \cos(m\pi x/L);$$

(2)

for  $0 \le z < \infty$ , and

$$\varphi_{2}(x,z) = b_{0} + c_{0}z + \sum_{m=1}^{\infty} \left\{ b_{m}e^{-(m\pi/L)z} + c_{m}e^{(m\pi/L)z} \right\} \cos(m\pi x/L);$$

(3)

for  $-h_1 \le z \le 0$ , respectively.

Results obtained from the full-wave analysis [6] have shown that the influence of the finite substrate thickness  $h_2$ - $h_1$  can be neglected for practical dimensions (i.e.,  $(h_2-h_1) >> h_1$ , s, w) for the case without ground plane.

In region of silicon substrate, which is assumed to be infinitely thick  $(h_2 \rightarrow \infty)$ , we may write the potential as

$$\varphi_1(x,z) = d_0 + \sum_{m=1}^{\infty} d_m e^{\left[\frac{m\pi}{L}(z+h_1)\right]} \cos(m\pi x/L);$$

(4)

for  $z \leq -h_1$ .

The different functional forms of the series expansions for potential distribution in the structure given by eqs. (2)-(4) are dictated by the boundary conditions.

# III. BOUNDARY CONDITIONS AND FREQUENCY-DEPENDENT LINE CAPACITANCE AND CONDUCTANCE CALCULATION

In order to determine the potential distribution in the structure the boundary conditions must be satisfied. At interface between dielectric layers, two boundary conditions need to be satisfied, i.e., the potential and the normal component of electric induction vector must be continuous. This leads to the following expression for the structure shown in Fig. 1:

$$b_m = \frac{1}{2} \left( 1 - \frac{\varepsilon_1}{\varepsilon_2} \right) e^{-m(\pi/L)h_1} d_m \quad \text{for} \quad m = 1, 2, \dots$$

(5)

$$c_m = \frac{1}{2} \left( 1 + \frac{\varepsilon_1}{\varepsilon_2} \right) e^{m(\pi/L)h_1} d_m \quad \text{for} \quad m = 1, 2, \dots$$

(6)

$$b_0 = d_0 \quad and \quad c_0 = 0.$$

(7)

The boundary conditions in the plane of the infinitesimally thin coplanar conductors at z=0 are slightly more complicated. Here, we require again that potential function  $\phi_i$  assume the same value on either side of the interface. This requirement leads to the following conditions

$$a_m = b_m + c_m$$

for  $m = 1, 2, ...$  (8)

$$a_0 = b_0. (9)$$

But the continuity of the normal component of the electric induction vector now holds only in the gaps between the coplanar conductors and not on the perfectly conducting interconnect conductors themselves. On the surface of the interconnect conductors the potential function need to be equal to the applied voltages V(x). We write the conductor potential as a function of x to indicate that its value is different on different conductors in the structure even though V(x) is constant on each conductor. Thus, we obtain using the relations (8) and (9), the following set of equations:

$$b_0 + \sum_{m=1}^{N-1} (b_m + c_m) \cos \left[ \frac{m\pi}{L} x_j \right] = V(x_j) \quad on \text{ the conductors}$$

(10)

$$\frac{L}{\pi}c_0 + \sum_{m=1}^{N-1} m \left[ \left( \frac{\varepsilon_3}{\varepsilon_2} - 1 \right) b_m + \left( \frac{\varepsilon_3}{\varepsilon_1} + 1 \right) c_m \right] \cos \left[ \frac{m\pi}{L} x_j \right] = 0 \quad in \ the \ gaps$$

(11)

The subindex j to the x coordinate means that we satisfy the boundary conditions in the conductor plane z = 0 only at a finite set of discrete points  $x = x_i$ , which may be chosen arbitrarily. In our case, for convenience, the discrete points are spaced equidistantly. There are N points in the conductor plane z = 0 if there are N terms in the series expansion in order to provide as many equations (one for each j) as we have unknown coefficients d<sub>m</sub>. It should be clear that the only remaining undetermined coefficients are the d<sub>m</sub>, since the a<sub>m</sub>, b<sub>m</sub> and  $c_m$  all depend unambiguously on  $d_m$  via eqs. (5)-(9). It is also important to note that the sets of equations (10) and (11) cannot be counted as furnishing 2N equations since (10) is used only on the conductor surfaces, while eq. (11) is used only in the interconductor space (gaps) at z = 0.

Point matching procedures simplifies the computational complexity considerably. There is no need for evaluating integrals over products of the potential V(x) with the orthogonal set of functions  $\cos[m(\pi/L)x]$ . Other methods of analysis [13, 15] require that the value of the voltage in the interconductor space be obtained by iteration, starting from a suitable initial choice. None of these complications occurs in the point matching procedure. We need only to compute the elements of the matrix  $\bf A$  in the equation system

$$\sum_{m=0}^{N-1} A_{jm} d_m = \begin{cases} V(x_j) & \text{on the conductors} \\ 0 & \text{in the interconductor gaps} \end{cases}$$

(12)

defined by relations (5) - (11). Inversion of the matrix leads to the computation of the unknown coefficients via

$$d_{m} = \sum_{j=0}^{N-1} (A^{-1})_{mj} \begin{cases} V(x_{j}) & on \text{ the conductors} \\ 0 & in \text{ the interconductor gaps} \end{cases}$$

(13)

Once the coefficients  $d_m$  are determined, the other expansion coefficients can be obtained using relations

(5) - (9) and the potential function distribution follows from (2) - (4), respectively.

Once the potential distribution is available, it is easy to calculate the capacitance (C) and conductance (G) per unit length of the examined transmission line structure. The lossy semiconducting substrate is taken into account by the complex permittivity

$$\varepsilon_{cs} = \varepsilon_s - j\frac{\sigma}{\omega} \tag{14}$$

where  $\varepsilon_s$  is the permittivity and  $\sigma$  conductivity of the semiconducting substrate (silicon).

Due to the quasi-TEM character of the electromagnetic fields in the examined structure the frequency dependent distributed admittance per unit length Y can be calculated as

$$Y = G + j\omega C = j\omega \frac{Q}{\Delta V}$$

(15)

where Q is the total charge per unit length and  $\Delta V$  denote the voltage difference between the conductors. Since we can calculate the capacitance and conductance per unit length of the examined structure very easily with the new procedure, all quasi-stationary propagation parameters of multiconductor transmission lines may be obtained.

### IV. Numerical Results

In order to demonstrate the suitability of the new formulation for the potential distribution computation, we present some examples. The numerical results and all graphs are calculated and constructed by computing the potential distribution at those x values that coincide with the points used for point matching; 150 terms are used in the series expansions.

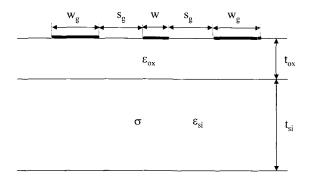

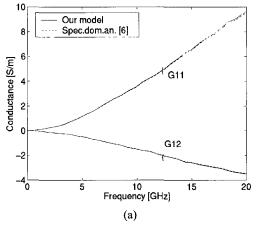

coplanar strip interconnects structure shown in Fig. 2 is considered. The technological and geometrical parameters of this structure are:

• w = 9.6

$$\mu$$

m, w<sub>g</sub> = 20  $\mu$ m, s<sub>g</sub> = 100  $\mu$ m, t<sub>ox</sub> = 0.58  $\mu$ m, t<sub>si</sub> = 500  $\mu$ m,  $\epsilon$ <sub>ox</sub> = 3.9  $\epsilon$ <sub>0</sub>,  $\epsilon$ <sub>si</sub> = 11.8  $\epsilon$ <sub>0</sub>,  $\sigma$  = 15.5 S/m.

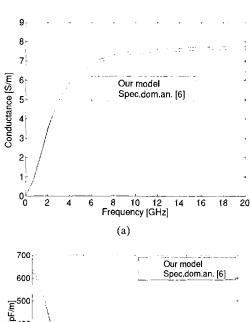

The frequency-dependent per unit length capacitance

and conductance parameters for coplanar strip interconnects structure are shown in Fig. 3.

Fig. 2. Symmetric coplanar strip interconnects configuration.

Fig. 3. The frequency response of (a) conductance per unit length and (b) capacitance per unit length. The solid lines in the figures are obtained with our model, and the dashed lines are the result from the spectral domain approach.

It can be seen that the frequency response calculated by using new formulation (point matching method with cosine Fourier series) is in very good agreement with that computed from the quasi-analytical analysis [6]. As expected, the lossy silicon substrate has a significant impact on the frequency-dependence of the line parameters of coplanar strip interconnect. It can be seen that the conductance per unit length G rapidly increases (see Fig. 3a) in the lower frequency range while the capacitance per unit length C decreases (see Fig. 3b).

### EXAMPLE 2

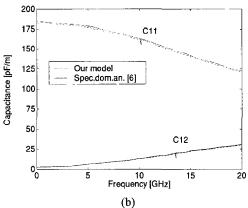

As the second application, the distributed capacitance and conductance per unit length for two coplanar coupled interconnect lines shown in Fig. 4 is considered.

This symmetric interconnect geometry has the following electrical and geometrical parameters:

• w = 2.0  $\mu$ m, w<sub>g</sub> = 20  $\mu$ m, s = 2.0  $\mu$ m, s<sub>g</sub> = 100  $\mu$ m, t<sub>ox</sub> = 0.50  $\mu$ m, t<sub>si</sub> = 500  $\mu$ m,  $\epsilon_{ox}$  = 3.9  $\epsilon_{0}$ ,  $\epsilon_{si}$  = 11.8  $\epsilon_{0}$ ,  $\sigma$  = 100 S/m.

Fig. 5. Self and mutual shunt admittance components: (a) conductance per unit length and (b) capacitance per unit length.

For comparison, the same symmetric coupled strip

coplanar interconnect problem is also rigorously solved by using spectral domain approach [6] with Chebyshev polynomial basis functions weighted by appropriate edge factors. The conductance and capacitance per unit length of the coupled interconnects are calculated by using our point matching method as a function of frequency (f = 0- 20 GHz), and compared with those of the spectral domain approach (full-wave solvers). We can see that the calculated results by our method are in very good agreement with the rigorous full-wave method solutions for whole frequency range. A comparison of the frequency response of the point matching-cosine Fourier series approach with that computed by the spectral domain technique [6] (Fig. 5a and b) shows that our approach yields very good results with little computation efforts.

### V. Conclusion

We have presented a point matching method and cosine Fourier series approach of single and coupled coplanar interconnect lines on lossy silicon substrate based on the quasi-stationary field analysis. Frequency-dependent values for the capacitance and conductance per unit length matrices have been calculated by a very simple formulation (no iterations needed) of the problem that is well suited for computer simulations with little programming effort.

## REFERENCES

- [1] Y. Eo and W. R. Eisenstadt, "High-speed VLSI interconnect modelling based on S-parameters measurements", IEEE Trans. Comp. Hybrids, Manuf. Technol., vol. 16, pp. 555 562, August 1993.

- [2] H. Hasegawa, M. Furukawa and H. Yanai, "Properties of microstrip line on Si-SiO<sub>2</sub> system", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-19, pp. 869 - 881, 1971.

- [3] H. Hasegawa and S. Seki, "Analysis of interconnection delay on very high-speed LSI/VLSI chips using an MIS microstrip line model", *IEEE Trans. Electron Devices*, vol. ED-31, pp. 347 - 352, March, 1984.

- [4] C. Warns, W. Menzel and H. Schumacher, "Transmission lines and passive elements for multilayer coplanar circuits on silicon", *IEEE Trans. Microwave Theory Tech.*,vol. MTT-46, pp. 616 - 622, May, 1998.

- [5] S. Zaage and E. Groteluschen, "Characterization of the

broadband transmission behaviour of interconnects on silicon substrates", *IEEE Trans. Comp. Hybrids, Manuf. Technol.*, vol. 16, pp. 686 - 691, November 1993.

- [6] E. Groteluschen, L. S. Dutta and S. Zaage, "Quasianalytical analysis of the broadband properties of multiconductor transmission lines on semiconducting substrates", *IEEE Trans. Comp. Pack. Manuf. Technol.*, Part B, vol. 17, pp. 376 - 382, August 1994.

- [7] R. Sorrentino, G. Leuzzi and A. Silbermann, "Characteristics of metal-insulator-semiconductor coplanar waveguides for monolithic microwave circuits", *IEEE Trans. Microwave Theory Tech.*,vol. MTT-32, pp. 410 -416, April, 1984.

- [8] T. C. Mu, H. Ogawa and T. Itoh, "Characteristics of multiconductor, asymmetric, slow-wave microstrip transmission lines", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 1471 - 1477, December, 1986.

- [9] T. Shibata and E. Sano, "Characterization of MIS structure coplanar transmission lines investigation of signal propagation in integrated circuits", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-38, pp. 881 - 890, July, 1990.

- [10] M. Aubourg, J. P. Villotte, F. Godon and Y. Garault, "Finite element analysis of lossy waveguides-application of microstrip lines on semiconductor substrate", *IEEE Trans. Microwave Theory Tech.*,vol. MTT-31, pp. 326 -331, April, 1983.

- [11] Y. R. Kwon, V. M. Hietala and K. S. Champlin, "Quasi-TEM analysis of 'slow-wave' mode propagation on coplanar microstructure MIS transmission lines", *IEEE Trans. Microwave Theory Tech.*,vol. MTT-35, pp. 545 -551, June, 1987.

- [12] J. Zheng, Y.-C. Hahm, V. K. Tripathi, and A. Weisshaar, "CAD-oriented equivalent-circuit modeling of on-chip interconnects on lossy silicon substrate", *IEEE Trans. Microwave Theory Tech.*,vol. MTT-48, pp. 1443 - 1451, September, 2000.

- [13] H. Ymeri, B. Nauwelaers and K. Maex, "Fast and accurate analysis of the multiconductor interconnects", in Proc. European Workshop Materials for Advanced Metallization (MAM 2000), pp. 142-143, 2000.

- [14] H. Ymeri, B. Nauwelaers, K. Maex, and D. De Roest, "Simple and accurate analysis of interconnects in high speed integrated circuits", *Microelectronic Engineering*, vol. 55, pp. 37 - 42, 2001.

- [15] H. Ymeri, B. Nauwelaers and K. Maex, "Computation of capacitance matrix for integrated circuit interconnects using semi-analytical Green's function method", *INEGRATION*, the VLSI journal, vol. 30, pp. 55 - 63, 2000.

- [16] D. S. Jones, Methods in Electromagnetic Wave Propagation. Oxford: Clarendon, 1979.

- [17] H. Davis, Fourier Analysis and Orthogonal Functions.

New York: Dover Publications, Inc., 1963.

Hasan Ymeri Was born in Druar near Mitrovicë, Kosovë on 24 October 1957. He received the Dipl. Ing. (M. Sc.) degree in electronic engineering from University of Prishtina, Prishtinë, Kosovë, in 1983, the Mag. Sci. degree in electrical engineering from the University of Ljubljana, Slovenia, in 1988, and the Dr.

Sc. degree in electronic engineering from the Polytechnic University, Tirana, Albania, in 1996, respectively. Since 1985 he has been with the University of Prishtina, first as Lecturer and later as Senior Lecturer, where has been involved in research on electromagnetic theory, microwave integrated circuits and digital electronics. At present he is with the Katholieke Universiteit of Leuven, Belgium, as a Researcher in the field of silicon IC interconnects.

Bart. K. J. C. Nauwelaers was born in Niel, Belgium on 7 July 1958. He received the M.S. and Ph. D. degrees in electrical engineering from the Katholieke Universiteit Leuven, Leuven, Belgium in 1981 and 1988, respectively. He also holds a Mastère degree from ENST, Paris, France. Since 1981 he has been

with the Department of Electrical Engineering (ESAT) of the K.U.Leuven, where he has been involved in research on microwave antennas, microwave integrated circuits, MMICs, and wireless communications. He teaches courses on microwave engineering, on analog and digital communications, on wireless communications and on design in electronics and in telecommunications

Servaas Vandenberghe was born in Leuven, Belgium, on March 31, 1972. He received a M.Sc. degree in electrical engineering from the Katholieke Universiteit (K.U.) Leuven, Belgium, in 1996. He is currently working towards a Ph.D. and is supported by the Institute for the Promotion of Innovation by

Science and Technology in Flanders (IWT). His main research interest is equivalent circuit based non-linear HEMT modelling.

Karen Maex received the M.S. degree in electrical engineering in 1982 and the Ph. D. degree in 1987 both from the Katholieke Universiteit Leuven, Leuven, Belgium. From 1982 until 1987 she has been a Research Assistant of the Belgian National Fund for Scientific Research (FWO). At present she is continuing her

research at the Interuniversity Microelectrics Center (IMEC) as a Research Director of the Fund for Scientific Research Flanders. She is a Professor at the E.E. Department of the Katholieke Universiteit Leuven. At IMEC she is Director of the Interconnect Technologies and Silicides (ITS) department within the Silicon Process Technology Division. Her interests are in materials science and technology for deep-sub-micron semiconductor devices.

**David De Roest** was born in Bruges on Sep. 24, 1975. He received the MS degree at the Department of Physical Engineering at the University of Ghent in 1998. He is currently working on a PhD in microelectronics at IMEC (Interuniversity Micro Electronics Center) Leuven. The research topic is electrical characterization

(low and high frequency) of low-k dielectrics and Cu interconnects.

Michele Stucchi was born in Bari, Italy. After the graduation in Electrical Engineering in 1988, he worked as process engineer in TI, Avezzano, Italy and as failure analysis engineer in Tecnopolis, Bari, Italy. Since 1996 he is at IMEC, Belgium, where he is currenly involved in the electrical characteriza-

tion of advanced Back-End architectures.