# Electrical and Chemical Properties of ultra thin RT-MOCVD Deposited Ti-doped Ta<sub>2</sub>O<sub>5</sub>

S. J. Lee, H. F. Luan, A. Mao, T. S. Jeon, C. h. Lee, Y. Senzaki, D. Roberts, and D. L. Kwong

Abstract - In Recent results suggested that doping Ta<sub>2</sub>O<sub>5</sub> with a small amount of TiO<sub>2</sub> using standard ceramic processing techniques can increase the dielectric constant of Ta2O5 significantly. In this paper, this concept is studied using RTCVD (Rapid Thermal Chemical Vapor Deposition). Ti-doped Ta<sub>2</sub>O<sub>5</sub> films are deposited using TaC<sub>12</sub>H<sub>30</sub>O<sub>5</sub>N, C<sub>8</sub>H<sub>24</sub>N<sub>4</sub>Ti, and O<sub>2</sub> on both Si and NH<sub>3</sub>-nitrided Si substrates. An NH<sub>3</sub>-based interface layer at the Si surface is used to prevent interfacial oxidation during the CVD process and post deposition annealing is performed in H<sub>2</sub>/O<sub>2</sub> ambient to improve film quality and reduce leakage current. A sputtered TiN layer is used as a diffusion barrier between the Al gate electrode and the TaTixOv dielectric. XPS analyses confirm the formation of a (Ta2O5)1-x(TiO2)x composite oxide. A high quality TaTi<sub>x</sub>O<sub>v</sub> gate stack with EOT (Equivalent Oxide Thickness) of 7Å and leakage current Jg=0.5A/cm<sup>2</sup> @ Vg=-1.0V has been achieved. We have also succeeded in forming a TaTi<sub>x</sub>O<sub>v</sub> composite oxide by rapid thermal oxidation of the as-deposited CVD TaTi films. The electrical properties and Jg-EOT characteristics of these composite oxides are remarkably similar to that of RTCVD Ta<sub>2</sub>O<sub>5</sub>, suggesting that the dielectric constant of Ta<sub>2</sub>O<sub>5</sub> is not affected by the addition of TiO<sub>2</sub>.

Index Terms - High K gate dielectric, Metal gate,

CMOS Fabrication process.

# I. Introduction

High dielectric constant materials such as Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, SrTiO<sub>3</sub>, (Ba,Sr)TiO<sub>3</sub> have been considered as a replacement for SiO<sub>2</sub> and SiN in future DRAM capacitors and MOSFET gate oxide applications [1-3]. Among them CVD Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> have received significant interests as a potential gate dielectric material for sub-100nm CMOS technology because of their high dielectric constant and excellent step coverage [4-5].

Recent results from Cava et al. [6] showed that the dielectric constant of  $Ta_2O_5$  can be enhanced significantly (by a factor of 4) by the addition of ~8%  $TiO_2$ . This would have considerable impact on future high-K gate dielectric technology. In their study, ceramic samples in the  $Ta_2O_5$ - $TiO_2$  system were made by standard ceramic processing technologies. In our study, attempts are made to apply this concept in a more manufacturable RTCVD process for the fabrication of a  $Ta_2O_5$  gate stack with the addition of controllable amount of  $TiO_2$ .

# II. EXPERIMENTS

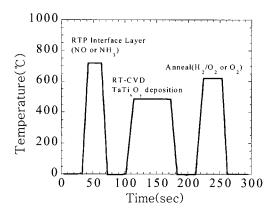

In our experiments, MOS capacitors with TaTi<sub>x</sub>O<sub>y</sub> dielectric were fabricated on p-type silicon wafer by *insitu* rapid-thermal multiprocessing whose temperature-time profile is shown in Fig 1. The bottom passivation layers were grown in NH<sub>3</sub> at 700°C for 10 s or in NO at 800°C for 20 s. An HF dip was applied after NO passivation processing to reduce the interface layer thickness. TaTi<sub>x</sub>O<sub>y</sub> films were deposited at 450°C for

Manuscript received August 12, 2001; revised September 7, 2001.

Microelectronics Research Center, Department of Electrical and

Computer Engineering, The University of Texas, Austin, TX 78712,

USA. SCHUMACHER, CALSBAD, CA 92009, USA 10100 Burnet

Road, MER 2.604 Bldg., Austin TX78758, USA

<sup>(</sup>e-mail:sungjoo@mail.utexas.edu) Tel: +1-512-471-4759

120sec by reacting  $TaC_{12}H_{30}O_5N$  and  $C_8H_{24}N_4Ti$  with  $O_2$  simultaneously using  $N_2$  as the carrier gas. Post deposition annealing was performed in  $H_2/O_2$  (50:50) at  $600{\sim}800{\circ}C$  for 30 s to improve film quality and reduce leakage current. An alternative approach was also used by depositing the Ta and Ti without  $O_2$  present, followed by RTP  $O_2$  oxidation. A TiN diffusion barrier was deposited on the  $TaTi_xO_y$  films by reactive sputtering and Al was used as a gate electrode.

**Fig. 1.** *In-Situ* RTP fabrication process for  $TaTi_xO_y$  gate stack dielectics.

The EOT is extracted from a simulation program considering quantum mechanical (QM) effects (7). The chemical properties of ultra-thin  $TaTi_xO_y$  films were investigated by *in-situ* XPS (X-ray Photoelectron Spectroscopy) in a separate CVD-UHV system. Deposition and annealing for XPS were carried out in a bench scale CVD reaction chamber (base pressure  $\sim 1x10^{-8}$  Torr) connected by a gate valve and sample transfer mechanism to a UHV (Ultra High Vacuum) XPS chamber (base pressure  $\sim 8x10^{-10}$  Torr). XPS data were taken with a cylindrical mirror analyzer at 25eV pass energy and analyzed for peak positions and peak areas.

#### III. RESULTS AND DISCUSSION

The interfacial layer between the high-K layer and Si is one of the key issues related to the development of high K dielectric stack. It was reported that ultra thin CVD  $Ta_2O_5$  (4) with an NO-grown oxynitride interface layer showed 3 orders of magnitude lower leakage current compared to the thermal oxide with same Tox,eq and superior interface quality. In this work,  $TaTi_xO_y$

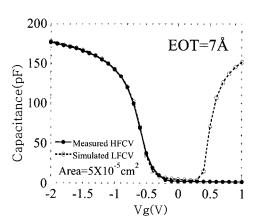

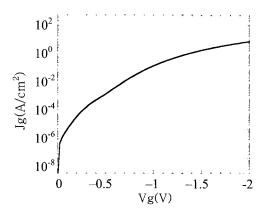

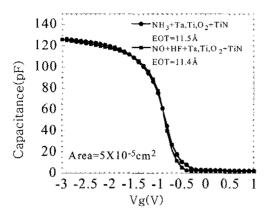

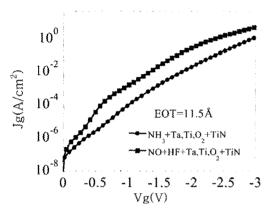

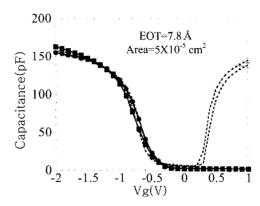

devices with an NO interface layer show a similar trend to Ta<sub>2</sub>O<sub>5</sub> devices as shown in ref [4]. In order to reduce EOT, an NH<sub>3</sub>-based interface layer is used instead of an NO interface layer. The NH<sub>3</sub>-based interface layer shows stronger resistance to oxygen diffusion during TaTi<sub>x</sub>O<sub>v</sub> deposition and post-deposition annealing and by using an NH3 interface layer, we obtained thinner films with EOT=7Å, Jg=0.5A/cm<sup>2</sup> @ Vg=-1V. Fig. 2 and Fig. 3 show the C-V (sweep rate: 500mV/sec) and I-V of this film. The Jg-EOT characteristics are quite similar to that of CVD Ta<sub>2</sub>O<sub>5</sub> films, suggesting that the addition of TiO<sub>2</sub> in our case may not have a major impact on the dielectric constant of Ta<sub>2</sub>O<sub>5</sub>, as reported in [6]. The high frequency C-V characteristics of TaTi<sub>x</sub>O<sub>y</sub> devices (EOT = 11.5Å) show that the NH<sub>3</sub>-based interface layer has similar good interface quality as an NO interface layer (Fig. 4). For the same EOT, the leakage current of the NH<sub>3</sub> interface devices is about one order of magnitude lower than that of devices with an NO interface layer (Fig. 5).

**Fig. 2.** HFCV of  $TaTi_xO_y$  film with NH<sub>3</sub> interface layer (EOT=7Å).

Fig. 3. I-V of TaTi<sub>x</sub>O<sub>y</sub> film with NH<sub>3</sub> nterface layer (EOT=7Å).

**Fig. 4.** HFCV of TaTi<sub>x</sub>O<sub>y</sub> film with NO and NH<sub>3</sub> interface layer.

Fig. 5. I-V of TaTi<sub>x</sub>O<sub>y</sub> film with NO and NH<sub>3</sub> interface layer.

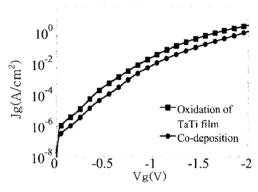

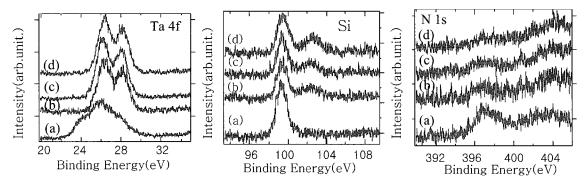

We have also studied the formation of TaTi<sub>x</sub>O<sub>y</sub> by introducing Ta, Ti precursors into the CVD chamber without O<sub>2</sub> present, followed by an RTP oxidation O<sub>2</sub> at 450~550°C. In Fig. 6 and Fig. 7, devices with post deposition oxidation are compared with co-deposition devices in terms of C-V and I-V characteristics. As shown in Fig. 5, for the same EOT, oxidation of TaTi devices show a little higher leakage current than codeposition devices. The resulting TaTixOv film after oxidation has similar stoichiometry to the co-deposited films with O2 present during deposition, stoichiometry of the films was obtained from peak areas of XPS spectra of Ta 4f, Ti 2p, and O 1s with consideration of atomic sensitivity factors, O 1s peak was deconvoluted to exclude oxygen signal from interfacial Si-oxide. However, N was detected in the asdeposited TaTix film, which was not completely removed even after 45s oxidation. The increase of leakage current in these films may be due to this residual N which was not found in conventional Ta, Ti, O2 co-deposition.

**Fig. 6.** Measured HFCV and simulated LFCV of  $TaTi_xO_y$  gate stack.

(solid circle: HFCV of co-deposition film, open circle:

LFCV of co-deposition film.

solid square: HFCV of oxidation of TaTi film, open square: LFCV of oxidation of TaTi film)

**Fig. 7.** I-V of TaTi<sub>x</sub>O<sub>y</sub> devices fabricated by co-deposition and post-deposition oxidation of TaTi films.

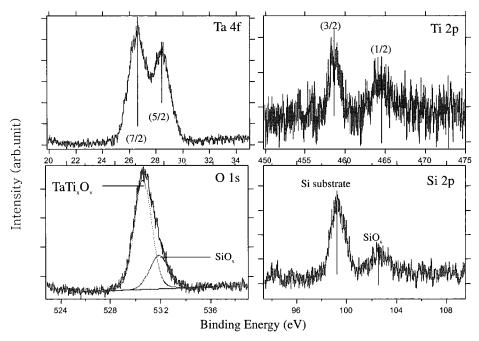

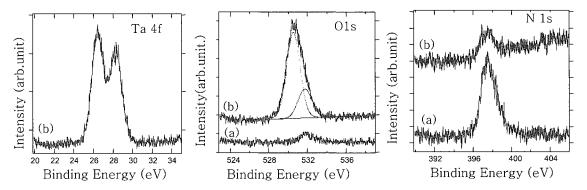

XPS analysis was performed on an as-deposited TaTi,O, film (Fig. 8), TaTi,O, deposited on NH,passivated film (Fig. 9) and Ta/Ti deposited film followed by oxidation (Fig. 10). From literature, Ta 4f (7/2) from Ta<sub>2</sub>O<sub>5</sub> peaks at 26.8eV and Ti 2p (3/2) from TiO, peaks at 458.8eV [8]. In Fig. 8, Ta 4f (7/2) and Ti 2p (3/2) peaked at 26.71 and 458.25 eV, respectively, suggesting that both Ta and Ti were not fully oxidized which could be attributed to the Ta-Ti bond. This observation indicates the CVD TaTi<sub>2</sub>O<sub>2</sub>(x~0.17, y~2.56) film is a composite oxide. The Si 2p peaks at 99.1eV represent the Si substrate and the second peak at 102.48eV represented non-stoichiometric Si oxide (SiO., x<2), compared with 103.3eV from fully oxidized Si (SiO<sub>2</sub>) [8]. The O 1s peak could be decomposed into two peaks - one from TaTi<sub>2</sub>O<sub>2</sub> and the other from SiO<sub>2</sub>. N Is spectrum (not shown) showed the as-deposited film

Fig. 8. XPS of Ta 4f, Ti 2p, O 1s, and Si 2p of TaTi<sub>x</sub>O<sub>y</sub> film deposition on clean Si(100) at 500 °C for 10 s.

Fig. 9. XPS of Ta 4f, O 1s and N 1s of  $TaTi_xO_y$  deposited on nitrided Si with NH<sub>3</sub> at 500 °C for 10 s(b); curves (a) are the XPS taken before  $Ta_2O_5$  deposition.

**Fig. 10.** XPS of Ta 4f, Si 2p, N 1s, and of (a) as-deposited  $TaTi_x$  film, followed by oxidation in  $O_2$  at (b) 450 °C for 30 s, (c) 45 s and (d) 75 s.

contained no N within the XPS detection limit. Fig. 9 shows the XPS of TaTi<sub>x</sub>O<sub>y</sub> deposited on NH<sub>3</sub>-passivated

Si at 500 °C for 10 s. A small O 1s peak, indicating some O incorporation in the nitride film, was from the

background during the nitridation. The N 1s peak position (397.5eV) was 0.1eV higher than that from  $Si_3N_4$  (397.4eV) (8), also indicating slight O incorporation. After film deposition, the nitrided Si was oxidized, resulting in the 8Å thicker SiO N (x~0.15. y~1.12). An alternative approach was implemented by depositing the film without co-dosing O, and followed by O<sub>2</sub> oxidation at relatively low temperature (< 500°C). As shown in Fig. 10, there was no evidence of SiO. formation from Si 2p spectrum after the deposition of TaTi<sub>x</sub>. SiO<sub>x</sub> was formed, due to the diffusion of O<sub>y</sub> during oxidation (Fig. 8 (b), (c), and (d)). There were at least two oxidation states in both Ta and Ti spectra for as-deposited TaTi. The Ta and Ti peaks at lower binding energies could result from the bonds with the precursor ligands. Nevertheless, those Ta and Ti components at lower binding energies were eliminated after oxidation in O<sub>2</sub> at 450°C for 30 s (Fig. 10 (b)). The resulting TaTi<sub>1</sub>O<sub>2</sub> after oxidation had similar stoichiometry as if the film were deposited directly with O2. However, N in the as-deposited TaTi, film still could not be completely removed, although reduced, even after additional 45 s of oxidation (Fig. 10 (d)), and finally removed by oxidation at 500°C for 30 s.

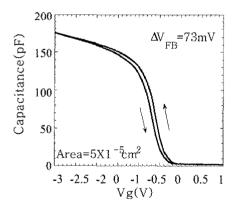

**Fig. 11.** Hysteresis characteristic of a TaTi<sub>x</sub>O<sub>y</sub> film with NH<sub>3</sub> interface layer.

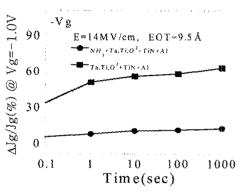

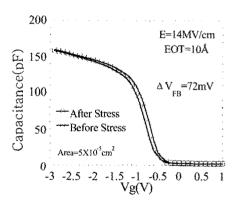

The hysteresis of the high frequency C-V of the  $TaTi_xO_y$  film was evaluated (Fig. 11). For the  $TaTi_xO_y$  film (EOT~7Å) with NH<sub>3</sub> interface layer and H<sub>2</sub>/O<sub>2</sub> annealing at 600°C for 60 s, the amount of V<sub>FB</sub> shift was 73mV. The SILC (Stress Induced Leakage Current) was measured under constant negative voltage stress with E=14MV/cm for 1000 s. For  $TaTi_xO_y$  with NH<sub>3</sub> interface

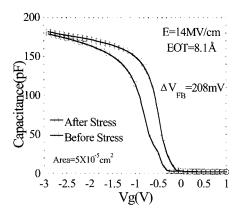

layer, the increase of leakage current due to stress was 11% (Fig. 12) and  $V_{FB}$  shifted 72mV (Fig. 12). In comparison, for  $TaTi_xO_y$  without interface layer, the increase of leakage current was 62% (Fig. 12) and  $V_{FB}$  shifted as much as 208mV (Fig. 14). This means that the  $TaTi_xO_y$  film without interface layer has more traps, which is believed to be due to sub-oxide grown at the interface (Fig. 8).

Fig. 12. Stress induced leakage current as a function of stress time for TaTi<sub>x</sub>O<sub>y</sub> with NH<sub>3</sub> interface layer and without interface layer.

Fig. 13. C-V curves of before and after constant voltage stress (E=14MV/cm) for  $TaTi_xO_y$  with  $NH_3$  interface layer.

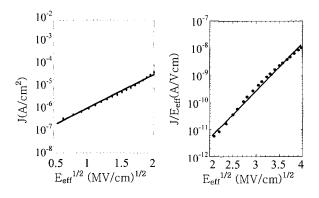

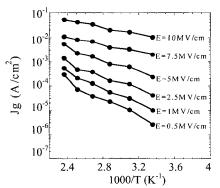

The conduction mechanism of TaTi<sub>x</sub>O<sub>y</sub> was studied by investigating the temperature dependence of the leakage current. The Schottky plot in Fig. 15 (a) and the Poole-Frenkel plot in Fig. 15 (b) show a linear relationship between Jg vs. E<sub>eff</sub><sup>1/2</sup> (E<sub>eff</sub>=Vg/Teq) at low electric field (E<2MV/cm), and a linear relationship between Jg/E<sub>eff</sub> vs. E<sub>eff</sub><sup>1/2</sup> at high electric field (E>2MV/cm). This indicates that the Schottky mechanism is dominant at low electric field and the Poole-Frenkel mechanism becomes dominant at high electric field [9]. Fig. 16 shows the temperature dependency of the leakage

current. At low electric field, leakage current shows more dependence on temperature, which supports the Schottky-type conduction mechanism in this region

Fig. 14. C-V curves of before and after constant voltage stress (E=14MV/cm) for  $TaTi_xO_y$  without interface layer.

**Fig. 15.** (a) Schottky plot of TaTi<sub>x</sub>O<sub>y</sub> with NH<sub>3</sub> interface layer (b) Poole-Frenkel plot of TaTi<sub>x</sub>O<sub>y</sub> with NH<sub>3</sub> interface layer.

Fig. 16. Temperature dependence of leakage current of  $TaTi_xO_y$  with  $NH_3$  interface layer.

# IV. Conclusion

Recent results suggested that doping Ta<sub>2</sub>O<sub>5</sub> with a

small amount of TiO<sub>2</sub> using standard ceramic processing techniques can increase the dielectric constant of Ta<sub>2</sub>O<sub>5</sub> significantly. In this paper, this concept is studied using RTCVD. Ti-doped Ta<sub>2</sub>O<sub>5</sub> films are deposited using TaC<sub>12</sub>H<sub>30</sub>O<sub>5</sub>N, C<sub>8</sub>H<sub>24</sub>N<sub>4</sub>Ti, and O<sub>2</sub> on both Si and NH<sub>3</sub>nitrided Si substrates. An NH3-based interface layer at the Si surface is used to prevent the interfacial oxidation during the CVD process and post deposition annealing is performed in H<sub>2</sub>/O<sub>2</sub> ambient to improve film quality and reduce leakage current. A sputtered TiN layer is used as a diffusion barrier between the Al gate electrode and the TaTi<sub>x</sub>O<sub>y</sub> dielectric XPS analyses confirm the formation of  $(Ta_2O_5)_{1-x}(TiO_2)_x$  composite oxide. High quality TaTi<sub>x</sub>O<sub>v</sub> gate stack with EOT=7Å and the leakage current Jg=0.5A/cm<sup>2</sup> @ Vg=-1.0V has been achieved. We have also succeeded in forming TaTi<sub>x</sub>O<sub>y</sub> composite oxide by RTP oxidizing as-deposited TaTi films. The electrical properties and Jg-EOT characteristics of these composite oxides are remarkably similar to that of RTCVD Ta<sub>2</sub>O<sub>5</sub> suggesting that dielectric constant of Ta<sub>2</sub>O<sub>5</sub> is not affected by the addition of TiO<sub>2</sub>.

#### REFERENCES

- [1] D. Park et al., *IEDM'98*, p. 381, 1998

- [2] Y. Momiyama et al., Symp. VLSI Tech. Dig., p. 135, 1997

- [3] Y. Ohno et al., Symp. VLSI Tech., p. 149, 1994

- [4] H. F. Luan et al., *IEDM'98*, p. 609, 1998

- [5] S. A. Campbell et al., IEEE Trans. Electron Devices, 44, 104, 1997

- [6] R. F. Cava et al., Nature, 377, 215, 1995

- [7] J. R. Hauser et al., Characterization and Metrology for ULSI Technology, p. 235, 1998

- [8] J. F. Moulder et al., Handbook of X-ray Photoelectron Spectroscopy, 1995

- [9] C. Chaneliere et al., J. Appl. Phys., 83, no. 9, p. 4823, 1998

Sungjoo Lee received the M. S. degree in electrical engineering from the University of Texas at Austin in 2000. He is currently pursuing the Ph. D. degree in the area of ultra thin gate oxides at the University of Texas at Austin, USA. He joined the Microelectronic Research Center of University of Texas in the Solid State Electronics divisions in 1998. His present interests and activities cover the development and characterization of advanced gate stacks for sub 100nm VLSI technologies and the study of reliability characteristics of high K gate dielectrics.

Hongfa Luan received the M. S. degree in the Institute of Semiconductor, Beijing, China, in 1986 and the Ph. D degree in the Beijing University of Science and Technology in 1991. He worked in Tsinghua University in Beijing, China from 1991 to 1996 as an associate professor. He joined the Microelectronic Research Center of University of Texas in the Solid State Electronics divisions in 1996 as a research fellow. He joined Radiant Photonics Inc. in 2001. Now, he is working in Teravicta Technologies Inc., Austin for developing MEMS.

**Taek Soo Jeon** was graduated from Hanyang University, Korea with B. S. degree in Materials Engineering in 1998. He received his M. S. degree in Materials Science and Engineering from the University of Texas of Austin in 2000. He is specialized in thin film characterization using surface analysis techniques. His recent research interests are high-k dielectric thin film on silicon.

Choong-Ho Lee was born in Korea in 1965. He received the B.S., in Electrical engineering from Inha University, Korea, in 1987. In 1988, he joined Samsung Electronics Company Ltd., Korea where he was involved in development of 64MSDRAM. And he received M.S. degree in 1999 and pursuing Ph.D. degree at the university of Texas at Austin. His current research interests are high-k gate dielectrics for sub-100nm CMOS device integration technology.

#### Y. Senzaki

The biography and photograph of Mr. Senzaki is not available.

#### D. Roberts

The biography and photograph of Mr. Roberts is not available.

Dim-Lee Kwong received his B.S. degree in physics and M.S. degree in Nuclear Engineering, both from the National Tsing Hua University, Taiwan, in 1977 and 1979, respectively. In 1982 he received the Ph.D. degree in Electrical Engineering from Rice University and received Best Dissertation Award. He

was an Assistant Professor of Electrical Engineering Department at the University of Notre dame during the years 1982-1985. He was a visiting Scientist at the IBM General Technology division. Essex Junction, Vermont during the summer of 1985 working on 4 Megabit DRAM technology. He joined The university of Texas at Austin, Microelectronics Research Center and Department of Electrical and Computer Engineering in 1985 as an Assistant Professor. He was promoted to associate Professor in 1986 and to Full Professor in 1990. Dr. Kwong received numerous awards including the IBM Faculty Development Award in 1984 and the Engineering Foundation Award from The University of Texas at Austin in 1994, holds the Earl N. and Margaret Brasfield Endowed fellowship, is the author of more than 210 referred journal and more than 200 referred conference proceeding publications, and has been awarded with more than 11 U.S. patents. His current areas of research interests include rapid thermal CVD technology for the growth and deposition of semiconductor materials compatible with ULSI processes, advanced dielectrics for logic, analog, and memory devices, metal gate electrode, shallow junctions, diffusion barrier materials and processes, and diffusion modeling of ion-implanted species during rapid thermal annealing.