# Study of Sol-Gel Prepared Phosphosilicate Glass-Ceramic For Low Temperature Phosphorus Diffusion into Silicon

Young Sig Kim

Department of Mineral and Energy Engineering

Chonnam National University, Kwangju 500-757, Korea

E-mail: youngkim@chonnam.ac.kr

(Received 13 February 2001, Accepted 28 April 2001)

A new solid source for low temperature diffusion into silicon was developed. The source wafer consists of an "active" compound, which is sol-gel prepared phosphosilicate glass-ceramics containing 56%  $P_2O_5$ , embedded in a skeletal foam-like, inert substrate. Phosphorus diffusion from the new solid sources at low temperatures (800-875° C) produced reprodecible sheet resistances and shallow junctions. From a series of one hour doping runs, the life time of the phosphosilicate source was determined to be over 40 hours. The effective diffusion coefficient of phosphorus into silicon and the corresponding activation energy at 850° C were determined to be  $7.5 \times 10^{-15}$  cm<sup>2</sup>/sec and  $\sim 3.9$  eV, respectively.

Keywords: Phosphosilicate Glass-Ceramic, Sol-Gel Process, Diffusion, Sheet Resistance.

### 1. INTRODUCTION

Solid sources in wafer or disk form are available for boron, phosphorus, and arsenic diffusions[1-4]. The solid source first developed was the boron nitride source, which was introduced by Goldsmith et al. in 1965[2]. The benefits of solid sources include excellent uniformity and reproducibility, and the ability of processing a large number of device wafers in a batch to reduce the manufacturing cost.

Several Solid sources have been developed for phosphorus diffusion. In 1976 Jones et al.[3] tested a solid source for phosphorus diffusion using silicon pyrophosphate (SiP<sub>2</sub>O<sub>7</sub>) as an active compound. Later versions consisted of porous ceramic wafers containing various concentrations of SiP<sub>2</sub>O<sub>7</sub> in an inert skeletal substrate wafer[5]. Solid sources using magnesium pyrophosphate (Mg<sub>2</sub>P<sub>3</sub>O<sub>7</sub>) and aluminum metaphosphate (Al(PO<sub>3</sub>)<sub>3</sub>) have been investigated as phosphorus sources for doping at temperatures 900° C and above[6].

As the IC complexity has advanced from small-scale integration to ultra-large scale integration (ULSI), the need for diffusion sources for small, shallow junctions and low temperature processing has increased. In this work, the doping performance, such as the sheet resistance and the junction depth, of sol-gel prepared phosphosilicate glass-ceramic containing 56 mol% of  $P_2O_5$  was evaluated as a low temperature

phosphorus diffusion source at temperatures, 825, 850, and 875° C.

# 2. EXPERIMENT

In this work, phosphosilicate glass-ceramic powder containing 56 mol% P<sub>2</sub>O<sub>5</sub> was prepared by a sol-gel process. Tetraethoxysilane(TEOS: Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>) and phosphoric acid were used as chemical precursors. TEOS and phosphoric acid were diluted with ethanol and mixed to form a gel. The gel was dried at  $\sim 45^{\circ}$  C, hand-ground, and heat treated at 500° C for four hours in flowing oxygen. The detail of the sol-gel procedure is presented elsewhere[7]. The heat treated powder was used as the active compound. This compound dissociates to yield phosphorus oxide vapor at the diffusion temperatures. The solid source consists of an active phosphorus compound embedded in a skeletal, foam-like. inert substrate which has excellent thermomechanical properties[8]. The substrate wafer is a high purity siliconized silicon carbide with an average porosity of 85-90%. The substrate wafer was infiltrated with a slurry containing active compound powder mixed with methanol, dried and fired to produce a sintered but porous material.

The silicon wafers are 3 inches in diameter, 13-15 mils thick, (100) oriented, p-type, 10-20 ohm/cm

resistivity. They were cleaned by the standard RCA cleaning procedure[9], and dipped in dilute HF prior to diffusion. The diffusion boat used for diffusion experiment was a standard four rail, fused silica boat, with 0.04 inch slots for the source wafers and 0.02 inch slots for the silicon wafers. The silicon wafers were arranged back-to-back and source wafers inserted between two silicon wafers at a surface-to-surface (dopant to wafer) spacing of 0.06".

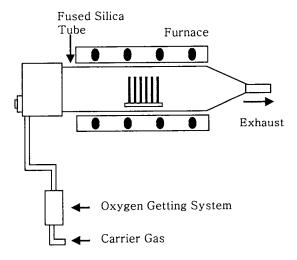

For the diffusion experiments, a 4-inch diameter fused silica tube furnace capable of maintaining a 10-inch long flat temperature zone was used. A "white elephant" fused silica tube extension was attached to the front of the diffusion tube to minimize contamination. The exit from the diffusion tube was connected to a water scrubbing system in order to remove any undesirable vapor in the exit stream before it was vented to an exhaust system. A schematic diagram of the diffusion furnace system is given in Fig. 1.

Fig.1. Schematic diagram of the diffusion furnace system.

The procedure for a diffusion run consisted of the following time cycles:

- 1. Place diffusion boat in white elephant and flush for 10 minutes with nitrogen flowing at 8 SLPM.

- 2. Push the boat into hot zone in about 5 minutes under above flow conditions.

- 3. Flush the system for 1 minute under above flow conditions.

- 4. Reduce the flow rate to 1.3 SLPM, and leave the boat in hot zone for required diffusion time.

- 5. Increase the flow rate to 8 SLPM and pull out the diffusion boat for 5 minutes.

- 6. Allow the boat to cool for  $\sim 15$  minutes.

Loading and unloading of the diffusion boat was carefully performed so as not to break the source and the silicon wafers by thermal shock. After a run was completed, the doped silicon wafers were taken out and stored in a nitrogen cabinet for further analysis.

The doping performance was evaluated by several parameters. Glass thickness and refractive indices were determined using an automated laser ellipsometer with 6328 Å wavelength. Sheet resistance data were obtained using a four-point probe method. The dopant distributions for selected wafers were determined using a Cameca IMS-3f ion microscopy. Positive cesium primary beams with beam acceleration energies of 3 and 12 KeV were used to bombard the surface. Junction depth measurements were made on selected wafers using a grooving-and-staining technique. A groove was cut in the silicon by rotating a diamond-grit impregnated wheel against the wafer.

#### 3. RESULTS AND DISCUSSION

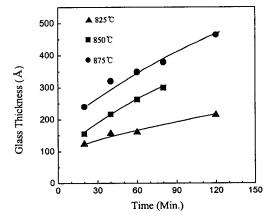

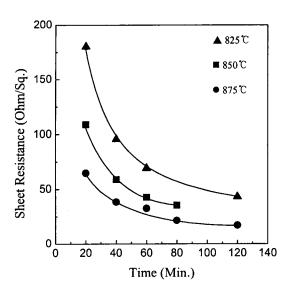

The effect of diffusion time on the phosphorus doping of silicon has been investigated in the temperature range 825 - 875 °C. The thickness of the glass deposited on the silicon wafer is plotted as a function of diffusion time at each temperature in Fig. 2. The glass thickness deposited from the phosphosilicate source increased as the diffusion time and the temperature increased. In Fig. 3, the sheet resistance data are plotted as a function of diffusion time. The sheet resistance are shown to decrease with increasing time and temperature.

For a constant source diffusion, the distribution of phosphorus in a diffused layer can be expressed as[10]:

$$C(x,t) = C_s \operatorname{erfc}(\frac{x}{2\sqrt{Dt}}) \tag{1}$$

where C(x,t) is the phosphorus concentration at point surface) at time t, Cs is the surface concentration, and D is the diffusion coefficient.

Fig. 2. Variation in glass thickness with diffusion time at 820, 850, and 875  $\,^{\circ}$ C.

For a diffused layer, the average value of sheet resistance  $(R_s)$  depends on the junction depth  $(x_j)$ , the impurity profile (C(x,t)), and the effective layer mobility  $\mu$  eff.

Fig. 3. Variation in sheet resistance with diffusion time at 825, 850, and 875  $\,^{\circ}$ C.

With these parameters, the sheet resistance can be written as[11]:

$$R_s = \frac{1}{q\mu_{eff} \int_{0}^{\infty} C(x,t)dx}$$

(2)

From equations (1) and (2) the sheet conductance, or the inverse of sheet resistance, can be expressed by a simple expression as:

$$R_s^{-1} = K\mu_{eff}C_s\sqrt{Dt}$$

(3)

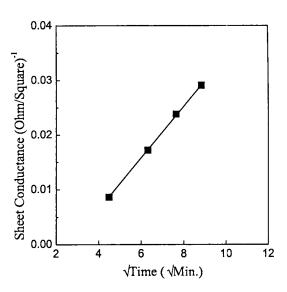

where K is a constant. Equation (3) shows that the sheet conductance is a linear function of the square root of time when the surface concentration is constant. The sheer conductance of the silicon doped at 850°C using the phosphosilicate source is plotted against the square root of time in Fig. 4. The sheet conductance are shown to be linearly proportional to the square root of time, which indicates that the surface concentration is constant.

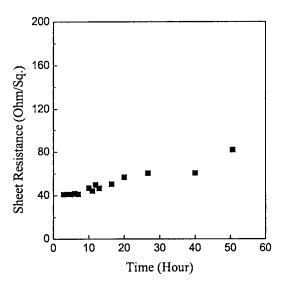

The run-to-run reproducibility which is an important factor for planar diffusion sources has been tested on the phosphosilicate sources. To examine the run-to-run reproducibility, a series of 1 hour diffusion runs was

Fig. 4. Sheet conductance versus square root of diffusion time.

Fig. 5. variation in sheet resistance with service time at 850  $\,^{\circ}$ C

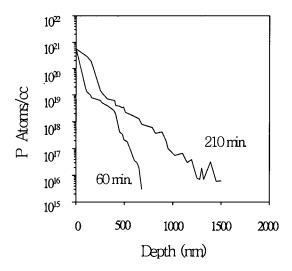

carried out at 850°C. In Fig. 5 the sheet resistances for 1 hour diffusion runs are presented against the service time. The sheet resistances from the phosphosilicate sources were nearly constant up to 40 hours of service time and began to increase slowly after that. It is suspected that phosphorus oxide is evaporated from the phosphosilicate source enough to saturate the surface concentration of the silicon up to 40 hours. The concentration profiles of phosphorus in silicon doped with 56 mol% source were measured using secondary ion microscopy(SIMS)

for quantitative analysis. The phosphorus profiles of silicon doped at  $850\,^{\circ}$ C are shown in Fig. 6. The surface concentration of the silicon doped at  $850\,^{\circ}$ C for 60 and 210 minutes are shown to be independent of time and to reach the solid solubility of phosphorus in silicon which is about  $5\times10^{20}$  atoms/cm<sup>3</sup>. This result is in good agreement with the sheet conductance plot shown in Fig. 4.

Fig. 6. SIMS profile of phosphorus in silicon doped for 60 and 210 minutes at 850 °C.

When the surface concentration is independent of time, the effective diffusion coefficient can be estimated from the junction depth measurement. As shown in Fig. 6, the phophorus concentration of the silicon doped at  $850^{\circ}$ C using the phosphosilicate source has reached the solid solubility limit and was independent of time. When the surface concentration is constant, the junction depth, Xj, can be expressed from equation (1) as:

$$X_{j} = 2\sqrt{Dt}erfc^{-1}(\frac{C_{sub}}{C_{s}})$$

(4)

where Csub is the substrate concentration.

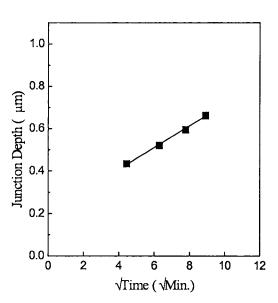

From the above equation, the junction depth should be a linear function of the square root of the diffusion time, and the slope of the straight line is the measure of the diffusivity of the dopant in silicon

$$\sqrt{D} = \frac{\frac{d(x_j)}{d(\sqrt{t})}}{2erfc^{-1}(\frac{C_{sub}}{C_s})}$$

(5)

The junction depth of the silicon doped at  $850^{\circ}$ C using the phosphosilicate source, as shown in Fig. 7, appears to be a linear function of the square root of time. From the slope of the plot, the surface concentration, and the substrate concentration( $1 \times 10^{15}$  atoms/cm³), the effective diffusion coefficient was determined to be  $7.5 \times 10^{-15} \text{cm}^2/\text{sec}$ . Diffusion coefficients reported in the literature are widely scattered. Fair and Tsai[12] reported the diffusion coefficient at  $900^{\circ}$ C to be  $\sim 10^{-17} \text{cm}^2/\text{sec}$ . Jones[3] determined the diffusion coefficient at  $950^{\circ}$ C to be  $2 \times 10^{-14} \text{cm}^2/\text{sec}$  using the junction depth data.

The diffusion coefficient can be expressed in the Arrhenius form as:

$$D = D_0 \exp(-\frac{E}{kT}) \tag{6}$$

where D0 is the frequency factor, E is the activation energy, k is the Boltzmann constant, and T is the temperature. From equations (4) and

(6), the activation energy can be expressed as:

$$E = -4.606K \frac{d(\log x_j)}{d(\frac{1}{T})}$$

(7)

Fig. 7. Junction depth versus square root of diffusion time at 850  $\,^{\circ}\mathrm{C}$

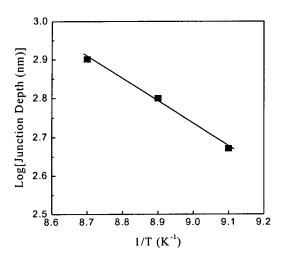

Equation (7) shows that the activation energy can be obtained from the slope of the Arrhenius plot of the junction depth. The Arrhenius plot of the junction depth of silicon doped with the phosphosilicate source

for one hour at 825, 850, and  $875^{\circ}$ C is present in Fig. 8. From the slope of plot the activation energy at above temperature range was obtained to be about 3.9 eV. Activation energies reported in the literature range from 3.3 to 4.4 eV[2,9].

Fig. 8. Arrhenius plot of the junction depth of silicon doped for 1 hour at 825, 850, and 875 °C.

## 4. SUMMARY

The evaluation of new solid diffusion source for low temperature diffusion of phosphorus into silicon using sol-gel prepared, 56 mol% phosphosilicate glass-ceramic powder as an active compound has been described. Preliminary diffusion experiment at 825-875 °C resulted in reproducible sheet resistances and shallow junction. It has been shown that the surface concentration has reached the solid solubility of phosphorus in silicon at 850 °C in 15 minutes.

The lifetime of the phosphosilicate solid source was determined from a series of one hour doping runs to be over 40 hours. From the junction depth data, the effective diffusion coefficient of phosphorus in silicon at  $850^{\circ}$ C and the corresponding activation energy were determined to be  $7.5 \times 10^{-15}$  cm<sup>2</sup>/sec and  $\sim 3.9$  eV, respectively.

#### **ACKNOWLEDGMENTS**

This work was supported in part by Namsun Industry Inc.

## REFERENCES

- [1] R.E. Tressler, J.J. Boeglin, J. Monkowski, J. Stach, G DeMunda, and C.Volk, *Solid State Tech.*, 27, 165, 1984.

- [2] N. Goldsmith, J. Olemstead, and J. Scott, Jr., RCA., 28, 344, 1967.

- [3] N. Jones, D.Metz, J. Stach, and R.E. Tressler, *J. Electrochem. Soc.*, 123, 1565, 1976.

- [4] D.Ruppercht and J. Stach, *J. Elcetrochem. Soc.*, 121, 722, 1974.

- [5] The Carborundum Company, Electronics Materials Div., Niagara Falls, New York 14302.

- [6] R.H.Kakkad, Study of Candidate Compounds for Phosphorus Solid Planar Diffusion Sources, M. S. Thesis, The Pennsylvania State University, 1986.

- [7] Y.S.Kim, R.E.Tressler, J. Mater. Sci., 29,2531, 1994.

- [8] M.O.Ten Eyck, M.R.Kasprzyk, and R.E.Tressler, "Foam Semiconductor Dopant Carriers," U.S.Patent No. 4,526,826, 1985.

- [9] W.Kern and D.A. Puotinen, RCA Rev., 31, 187, 1970.

- [10] S.M.Sze, Semiconductor Devices Physics and Technology, p. 386, John Wiley & Sons, 1985.

- [11] J.C.C.Tsai in "VLSI Technology" (S.M.Sze Ed.), p. 186, McGrqw-Hill, 1983.

- [12] R.B.Fair and J.C.C. Tsai, J. Electrochem. Soc., 124, 1107, 1977.