# Efficient Computation of the DFT and IDFT in Communication Systems Using Discrete Multitone Modulation

Antoni Fertner, Mattias Hyll, and Anders Örling

Abstract: The Discrete Fourier Transform (DFT) and the Inverse Discrete Fourier Transform (IDFT) are commonly used in signal processing applications, in particular in digital communication systems using the multi-carrier modulation principle. In such systems an IDFT is computed at the transmitter end, and a DFT at the receiver end. This paper examines a technique of computations, for which only negligible differences appear between the DFT and the IDFT calculations while the number of arithmetic operations required is substantially reduced. This offers significant advantages for the design of an IDFT/DFT processor for Discrete Multitone (DMT) systems.

Index Terms: Discrete Fourier Transforms, Fast Algorithms, DSP Applications, Communication Systems.

### I. INTRODUCTION

The transmission of high-speed data can be accomplished through the use of Discrete Multitone (DMT) modulation. The modulating/demodulating process is implemented very efficiently using the Inverse Discrete Fourier Transform (IDFT) for modulation and the Discrete Fourier Transform (DFT) for demodulation [1]. An efficient method for mapping the DFT and IDFT computations to a computing device is presented. Hermitian symmetry of the transmitted sequence in the frequencydomain, imposed by the DMT protocol, may be exploited to effectively reduce the number of arithmetic operations. The Hermitian symmetry yields a real transmitted waveform in the time domain. Hence, the DFT of a 2N-point real input sequence can be obtained from computation of one N-point complex data DFT at the receiving end. In Section II, we demonstrate that an algorithm having the same structure can be used at the transmitting end, to generate a 2N-point real output sequence directly from the N-point complex sequence. In Section III we demonstrate that the standard FFT algorithm is preceded and succeeded by identical data manipulations which yield the DFT and IDFT. This simplifies the actual implementation, which is discussed further. The conclusions are presented in Section IV.

Manuscript received December 7, 1998; approved for publication by Giuseppe Caire, Division I Editor, March 11, 1999.

A. Fertner and M. Hyll are with Ericsson Telecom AB, Access Application Lab, S-126 25 Stockholm, Sweden, e-mail: etxafer@kk.etx.ericsson.se and mattias.hyll@etx.ericsson.se.

A. Örling is with ÅF Industriteknik AB, Skalholtsgatan 2, P.O. Box 35 SE-164 93 Kista, Sweden, e-mail: andcrs.orling@ind.af.se,

# II. COMPUTATION OF THE 2N-POINT REAL IDFT OF AN N-POINT COMPLEX SEQUENCE

We assume the following definition of the DFT/IDFT pair throughout the paper:

$$X_k = \sum_{n=0}^{2N-1} x_n \cdot W_{2N}^{kn}, \qquad k = 0, 1, \dots, 2N - 1, \quad (1)$$

$$x_n = \frac{1}{2N} \sum_{n=0}^{2N-1} X_k \cdot W_{2N}^{-kn}, \quad n = 0, 1, \dots, 2N - 1,$$

(2)

where  $W_{2N} = e^{-j\frac{2\pi}{2N}}$ .

The algorithm which permits the efficient computation of the DFT of a real sequence is widely known in literature [2], [3]. The sequence is arranged so that even samples form the real part and odd samples the imaginary part of a complex sequence of half the length. This sequence is then transformed using the standard FFT routine. A similar algorithm can be derived to generate a 2N-point real output sequence directly from the N-point complex sequence at the transmitted end. Forced Hermitian symmetry implies that

$$X_{N+k} = X_{N-k}^*. (3)$$

Introduce the complex series  $v_n$

$$v_n = x_{2n} + j \cdot x_{2n+1},\tag{4}$$

where  $n=0,1,\cdots,N-1$  , and the real series,  $x_n$  , is the IDFT of  $X_k$ .

The real part of  $v_n$  may be expressed as

$$\operatorname{Re}\{v_n\} = x_{2n} = \frac{1}{2N} \sum_{k=0}^{2N-1} X_k \cdot W_{2N}^{-k2n}$$

$$= \frac{1}{2N} \sum_{k=0}^{2N-1} X_k \cdot W_N^{-kn}.$$

(5)

After straightforward manipulation one obtains

$$\operatorname{Re}\{v_n\} = \frac{1}{2N} \sum_{k=0}^{N-1} (X_k + X_{N-k}^*) \cdot W_N^{-kn}.$$

(6)

Similarly, the imaginary part of  $v_n$  may be expressed as

$$\operatorname{Im}\{v_n\} = \frac{1}{2N} \sum_{k=0}^{N-1} \left\{ (X_k - X_{N-k}^*) \cdot W_{2N}^{-k} \right\} \cdot W_n^{-kn}. \tag{7}$$

Consequently, computation of the series  $v_n$  involves one N -point IDFT

$$v_n = \frac{1}{N} \sum_{k=0}^{N-1} \hat{X}_k \cdot W_N^{-kn}.$$

(8)

where the  $\hat{X}$  sequence is expressed as

$$\hat{X}_k = \frac{1}{2}(X_k + X_{N-k}^*) + \frac{j}{2}(X_k - X_{N-k}^*) \cdot W_{2N}^{-k}.$$

(9)

Hence by simply separating the real and imaginary parts, i.e., assigning the real part of the resulting series,  $v_n$ , to the even-numbered samples, and the imaginary part to the odd-numbered samples, we obtain the desired real sequence  $x_n$ .

Since the DFT and IDFT are half as long as the original sequences the algorithm requires  $N/2 \cdot (log_2N+1)$  complex multiplications and  $N \cdot (log_2N+2)$  complex additions, whereas executing the standard FFT requires  $N \cdot (log_22N-1)$  complex multiplications and  $2N \cdot (log_22N-1)$  complex additions [2], [3].

## III. IMPLEMENTATION

The algorithm described in [2], for the efficient computation of the DFT of a 2N-point real sequence, and the algorithm described by (8) and (9) fall into a common scheme, which may be summarized as follows:

- I. manipulation of the input block data,

- 2. execution of the standard FFT routine,

- 3. manipulation of the resulting output block data.

However, the IDFT can be expressed in terms of the DFT [2]-[4]

$$IDFT(X_k) = \frac{1}{2N} [DFT(X_k^*)]^*.$$

(10)

therefore Step 2 requires executing the standard FFT routine, while the complex conjugates can be directly incorporated into data manipulation Steps 1 and 3.

In the case of transforming the real sequence, the input data manipulation consists of arranging the sequence so that the even samples form the real part, and the odd samples the imaginary part, of a new complex sequence. In the case of transforming the Hermitian- symmetric sequence, the input data manipulation is described by (9), except for the additional complex-conjugate following from the property, (10). This results in

$$\hat{X}_k^* = \frac{1}{2}(X_k^* + X_{N-k}) - \frac{j}{2}(X_k^* - X_{N-k}) \cdot W_{2N}^k.$$

(11)

The output data manipulation in the case of transforming the real sequence according to [2] consists of computing:

$$\hat{X}_{k}^{*} = \frac{1}{2}(X_{k}^{*} + X_{N-k}) - \frac{j}{2}(X_{k}^{*} - X_{N-k}) \cdot W_{2N}^{k}, \quad (12)$$

where  $X_k$  is the DFT of the N-point complex sequence created from the real sequence,  $x_n$ . Comparing (11) with (12) reveals that they exhibit identical structures.

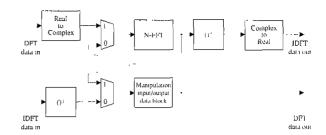

Fig. 1. Block diagram of the proposed DFT/IDFT algorithm. Multiplexer position '0' corresponds to calculating IDFT: multiplexer position '1' - to calculating the DFT.

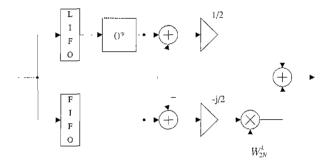

Fig. 2. Structure of the input/output data manipulation block.

The output data manipulation resulting from the transforming of the Hermitian-symmetric sequence consists of rearranging the sequence, so that the real part of a complex sequence is assigned to even samples, and the imaginary part to the odd samples, i.e. the same operations as the input data manipulation for transforming the real sequence, but executed in reversed order. A conceptual block diagram for the resulting structure is shown in Fig. 1.

The idea of the proposed approach is to reduce the size of the standard FFT routine while applying identical data manipulation scheme for computing DFT and IDFT in DMT application. The structure of the "manipulation block" of Fig. 1 is described by (11) and (12) and illustrated in Fig. 2. The FIFO (First In First Out) and LIFO (Last In First Out) blocks are buffers which provide read-out sequences for data in direct and reversed order.

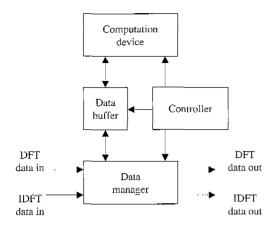

The relevant blocks of the implementation structure are: a computation device, a data manager, a controller and a buffer or set of buffers, which are shared between the computation device and data manager as illustrated in Fig. 3. The computation device performs the calculations. The data-manager block manipulates input and output data. The controller synchronizes the process by sending control signals to all participating blocks. The data-manager block collects the data appearing sequentially at the input indicated by the controller. If the DFT input is selected, the input sequence is real and the samples appear at the system sampling frequency. The data manager forms complex numbers from two subsequent samples, and stores these in the shared buffer. If the IDFT input is selected, the input sequence is complex and is stored directly in the shared buffer. The data-manager also outputs the already computed DFT from the shared buffer to the selected output. If the IDFT output is selected, the data manager forms a real sequence from the com-

Fig. 3. The implementation structure of the proposed DFT/IDFT algorithm.

puted complex sequence. If the DFT output is selected, it puts the numbers directly to the output. Another function of the data manager is to handle the digit-reversal properties of the FFT algorithm. This can be done without cost in terms of storage area and latency, if every second DFT or IDFT is computed with digit-reversed input data, and the others, with naturally-ordered input data. The implementation of a function of this nature would typically be done with either a standard DSP chip or chip set, or with an ASIC chip specific to the application. If an ASIC implementation is chosen only minor extensions to the data path is required, and for a DSP implementation, a DSP suited to butterfly operations should perform the manipulation operation.

### IV. CONCLUSION

The method for the efficient computation of the DFT (IDFT) of real-valued sequences is very well known and is often referred in technical literature. It permits the size of the DFT to be reduced thus saving a number of arithmetical operations. In this paper we have presented an algorithm exploiting the hermitian symmetry imposed by the DMT communications protocol. The proposed algorithm enhances the efficiency of the FFT algorithms by reducing the size of the FFT by a factor of two with only a small number of additional computations. The fact that the algorithm at the transmitting and receiving end has the same structure, significantly reduces the cost of a DMT transceiver. An efficient method for mapping the DFT and IDFT computations to a single computing device is presented in this paper.

# **ACKNOWLEDGEMENTS**

We owe special thanks to John R. Lastova of Nixon & Vanderhye PC for valuable comments and many helpful suggestions. We wish to thank the anonymous reviewers for their valuable comments, which led to substantial improvements in the paper presentation.

### REFERENCES

- [1] A. Ruiz, J. M. Croffi, and S. Kasturia, "Discrete multiple tone modulation with coset coding for the spectrally shaped channel," *IEEE Trans. Com*mun., vol. 40, no. 6, pp. 1012–1029, Feb./Mar./Apr. 1995.

- [2] J. G. Proakis and D. G. Manolakis, Digital Signal Processing, Macmillan Publishing Company, 1992.

- [3] P. Duhamel and M. Vetterli, "Fast Fourier transforms: A tutorial review and state of the art," Signal Processing, vol. SP-19, no. 4, pp. 259–299, Apr. 1990.

- [4] Patent JP-08163074 "Digital signal processor built with digital signal modulator and demodulator combines assembly of fast Fourier transformation unit, controller and memory in one integrated circuit."

Antoni Fertner received M. Sc. degree in electrical engineering from the University of Mining and Metallurgy, Cracow, Poland, in 1973 and the Ph. D. degree in radioelectronics from the Technical University of Warsaw, Poland, in 1978. From 1973 to 1978 he was with the Institute of Nuclear Physics and Techniques at University of Mining and Metallurgy, Cracow. In 1978 he joined the Research Institute for Catalysis and Physico-Chemistry of Surface at Polish Academy of Sciences, Cracow. Since 1981 he was employed by Institute of Microwave Technology at the Royal Institute of Microwave Technology at the Royal Institute

tute of Technology, Stockholm, Sweden, Swedish Institute of Microelectronics, Kista, and Catella Generics AB, Kista. He joined Ericsson Telecom AB, Stockholm, in 1991 where he holds a position of expert in numerical analysis and optimization. He is currently involved in various areas of communication research.

Mattias Hyll received the M. Sc. degree in electrical engineering from the Royal Institute of Technology, Stockholm, Sweden, in 1996. He joined Ericsson Telecom AB, Stockholm, in 1996 where he holds a position as a research engineer. He is currently involved in various areas of communications research.

Anders Örling received a M. Sc. degree in electrical engineering from the Royal Institute of Technology, Stockholm, Sweden. in 1994. From 1994 to 1998 he was with Ericsson Telecom AB, Stockholm. In 1998 he joined AB Ångpanneföreningen, Kista, Sweden, and is currently involved in various research and development projects within telecommunication systems.