## Design and Process of Vertical Double Diffused Power MOSFET Devices

# (二重擴散 方法에 依む 垂直構造形 電力用 MOSFET의 設計 및 工程)

劉賢奎,權相直,李仲煥,權五準,康英一

(Hyun Kyu Yu, Sang Jik Kwon, Joong Whan Lee, Oh Joon Kwon and Young Il Kang)

#### 要 約

이중확산공정에 의한 수직구조의 전력 MOSFET (VDMOS)를 설계 및 제작하고 그 성능에 대하여 기술하였다. 안타몬 (Sb)이 약  $7 \times 10^{17}$  cm  $^3$  도우핑된 초기 실리콘기판(N $^*$ ) 위에 비저항 약  $12\Omega$ -cm, 두께  $32\mu$ m의 에피층(N $^-$ )을 성장시켰다. 폭  $21\mu$ m의 폴리실리콘에 의해  $P^-$  및 N $^*$  확산공정을 자기정렬(selfalign) 방식으로 수행하여 게이트 및 소오스를 형성하였고, 이때  $P^-$ 채널 길이를  $1 \sim 2\mu$ m 정도로 조정하였다. 도통저항(on-resistance,  $R_{on}$ )을  $1\Omega$ 정도 유지시키면서 소자의 항복전압을 증가시키기 위하여 세겹의  $P^*$  확산때 (guard ring)를 칩 주변에 배치하였다. 칩 면적  $4800\mu$ m $\times$   $4840\mu$ m인 전력 MOSFET는 항복전압  $410\sim440$ V, 허용전류 5A이상,  $R_{on}$   $1.0\sim1.2\Omega$ 의 특성을 보였다.

#### Abstract

The design, fabrication and performance of a vertical double diffused power MOSFET (VDMOS) were described. On the antimony (Sb) doped ( $\sim$ 7x10<sup>17</sup> cm<sup>-3</sup>) silicon substrate (N<sup>+</sup>), epitaxial layer (N<sup>-</sup>) was grown. The thickness and the resistivity of this layer were 32 $\mu$ m and about 12 $\Omega$ -cm, respectively. The P<sup>-</sup> channel length which was controlled by sequential P<sup>-</sup>/N<sup>+</sup> double diffusion method was about 1 $\sim$ 2  $\mu$ m, and was processed with the self alignment of 21  $\mu$ m width poly silicon. To improve the breakdown voltage with constant on-resistance (R<sub>on</sub>) about 1 $\Omega$ , three P<sup>+</sup> guard rings were laid out around main pattern. With chip size of 4800  $\mu$ m x 4840  $\mu$ m, the VDMOS has shown breakdown voltage of 410 $\sim$ 440 V, on- resistance within 1.0 $\sim$ 1.2 $\Omega$  and the current capability of more than 5A.

#### I. Introduction

Until recently, silicon bipolar transistor is the major active components of medium

to high frequency power amplification and switching applications due to a high average chip current density and good geometrical control of the active transit region width [1,2].

However, field effect transistors (FET's) offer several attractive features as high power devices [3-7]. First, these devices have a high switching speed due to the absence of minority carrier storage effect. Second, these devices

(Electronics and Telecommunications Research Institute)

接受日字: 1986年 8月 20日

<sup>\*</sup>正會員,韓國電子通信研究所

have a higher input impedance than bipolar transistors, which greatly simplifies the gate drive circuit. In addition, the negative temperature coefficient of the drain current in these devices allow their operation to be in parallel without the thermal runaway problem that is prevalent in bipolar transistors. Further, since these transistors are majority carrier devices, the processing of these devices dose not require the stringent controls on the minority carrier lifetime that is necessary during the fabrication of bipolar transistors. These superior capabilities has arisen primarily through the use of double diffusion techniques to achieve short active channels and the incorporation of a lightly doped drift region between the channel and the drain contact, which largely supports the applied voltage.

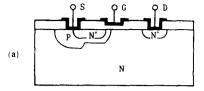

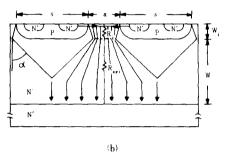

Many different structures have been proposed to implement these new devices such as the lateral double diffused transistor (LDMOS), the vertical double diffused transistor (VDMOS), and the V-groove double diffused transistor (VMOS). The three DMOS structures are shown in cross section in Fig. 1.

The choice of (100) material for LDMOS and VDMOS provides the improvement in electron inversion layer mobility and electron scattering limited velocity. These effects result in lower channel resistance and higher device transconductance per unit width in the LDMOS and VDMOS structures. The VMOS is constrained to have its channel along an etched (111) surface [8]. For this reason, VMOS may itself brings on higher Qf that causes impact on other device parameters such as noise performance in linear amplifications. Other disadvantages of the nonplanar device are the fabrication difficulties in terms of metal coverage and photolithography. On the otherside, the VMOS and VDMOS structures require only two of the electrodes on the top surface. This would tend to indicate that they should be capable of higher packing density than the LDMOS which has the drain connection on the top surface [9]. these effects into consideration, VDMOS has been adapted to be the best for achieving high breakdown voltages as well as high current handling capability.

This paper describes the VDMOS power

Fig. 1. Cross sections of three high voltage DMOS devices.

- (a) LDMOS,

- (b) VDMOS,

- (c) VMOS.

transistor using silicon gate MOS IC technology. The design and the process parameters are optimized to provide  $410\sim440\text{V}$  drain-source breakdow, voltage with more than 5 A drain current and  $1.0\sim1.2\Omega$  on-resistance.

#### II. Design and Fabrication

#### 1. Design Considerations

The N<sup>-</sup> epi-layer should be so much thick and high-resistive to be depleted far enough before avalanch breakdown occurs. That is for advancing the source-drain breakdown voltage. The source is shorted to P-well. However, too much thick and high-resistive N<sup>-</sup> epi-layer also raises on-resistance, R<sub>on</sub>. For these reasons the most important design

trade-off for power MOSFET's is that between on-resistance and breakdown voltage.

A proper design procedure of the power MOSFET and the minimization of the ideal  $N^-$  epitaxial layer resistance for a given desired breakdown voltage  $V_B$  (100~1000V range) have been discussed by C. Hu et al. [10]. Assuming a uniform doping level in the  $N^-$  epi-layer, the optimum thickness W, and the resistivity  $\rho$  are

$$W = 1.74 \times 10^{-6} \times V_B^{1.2} \text{ cm}$$

(1)

$$\rho = 4.55 \times 10^{-3} \times V_{R}^{1.3} \Omega \cdot cm.$$

(2)

Using (1) and (2) we chose W and  $\rho$  as 25.5  $\mu$ m and 12  $\Omega$ -cm respectively to obtain 400 V breakdown characteristics with 10% safety margin.

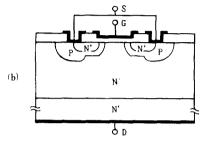

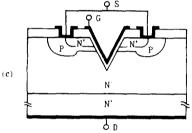

The on-resistance  $R_{\rm on}$  is determined by a series combination of several elements (Fig. 2-(a))<sup>[10]</sup>. For a high voltage device, the largest contribution to  $R_{\rm on}$  is the resistance of the epitaxial layer below the gate

$$R_{epi} = R_{ideal} \cdot \gamma_{epi} = \rho \cdot \frac{W}{A} \gamma_{epi}$$

(3)

where A is the total active device area,  $\gamma_{\rm epi}$  is the spreading resistance factor.  $\gamma_{\rm epi}$  has been estimated with 45° spreading-angle model for linear geometry [10].

JFET resistance  $(R_j)$  was considered as the second element of  $R_{OR}$  by the presence of parasitic JFET between adjacent P wells as shown in Fig. 2-(b). A trapezoid model is used for the calculation of  $R_j$ . If the depletion region width is negligible compared to well spacing,  $R_i$  can be predicted as

$$R_{j} = \frac{\rho \cdot W_{j}}{a/(s+a)} \frac{1}{A}$$

(4)

where  $W_j$  is the junction depth of the well and s is the well width. When the ratio of neck area to cell area is less than 40%, the other elements are much smaller than  $R_{epi} + R_j$ . The total on-resistance can be written

$$R_{on} \simeq R_{epi} + R_j \tag{5}$$

To meet fabrication compatibility and

Fig. 2. (a) The four components of on resistance are shown for a power VDMOS transistor.

(b) Definition of R<sub>j</sub> and R<sub>epi</sub>. Current is assumed to flow within α<sup>o</sup> spreading-angle. The narrowest part is the neck of the JFET.

minimization of  $R_{ON}$  ( $<1\Omega$ ) with fixed  $\rho$  and W, we chose the ratio of neck area to cell area as 30%. Design rules for the device was  $6\mu m$  minimum feature sizes and  $2\mu m$  alignment tolerances. Considering that lateral diffusion length is  $4\mu m$  by double diffusion technology, we set poly width and poly to poly distance all  $21\mu m$ . This paper adapted the stripe cell geometry which has  $7\mu m \times 7\mu m$  contact size.

To improve the breakdown voltage with constant on-resistance,  $P^+$  guard rings were applied around the active region [11]. Three guard rings were each apart from active region  $20\mu m$ ,  $50\mu m$ ,  $84\mu m$ , respectively, and their widths were all the same as  $10\mu m$ . The edge of the 3rd guard ring was surrounded by equipotential metal line for channel stopping which has gap as  $34\mu m$ .

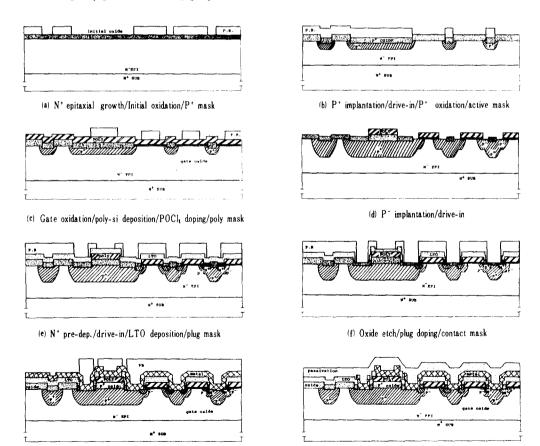

#### 2. Device Fabrication

In Fig. 3, the VDMOS fabrication steps are shown. Highly doped Sb ( $\sim$ 7 x  $10^{17}$  cm<sup>-3</sup>), N<sup>+</sup> substrates were used; the N<sup>-</sup> layers were grown with conventional epitaxial techniques. The thickness and the resistivity of the epitaxial layer were approximately  $32\mu$ m and  $12\Omega$ -cm respectively.

An initial SiO<sub>2</sub> film was grown with 2000 A thickness (Fig. 3-(a)). After delineating the P<sup>+</sup> region and etching away the film, boron implantation of 3 x 10<sup>14</sup> cm<sup>-2</sup> dose was performed using 100 KeV energy. The drive-in for the boron and P<sup>+</sup> doped oxide growing were carried at 1150°C for 60 minutes in N<sub>2</sub> gas and at 950°C for 150 minutes in wet O<sub>2</sub> ambient respectively. The resulting P<sup>+</sup> oxide thickness was 5000Å (Fig. 3-(b)). And then defining of the active region, gate oxidation, poly silicon

(g) Metal deposition/metal mask

deposition and poly doping process were followed. The gate oxide was thermally grown to a thickness of 1500 Å using C<sub>2</sub> HCl<sub>3</sub>/O<sub>2</sub> ambient at 1000°C for 200 minutes. Poly silicon deposited at 625°C with 5500 Å thickness, was doped with phosphorus under POCl<sub>3</sub> at 950°C (Fig. 3-(c)). After delineating poly silicon gate by dry etching, boron implantation (P implantation) and gate oxide layer etching were carried successively. P implantation was processed by 1 x 10<sup>14</sup> cm<sup>-2</sup> of boron using 80 KeV energy. P diffusion was performed at 1150°C for 720 minutes. The P oxide was grown to a thickness of 1500 Å (Fig. 3-(d)). Removing P oxide carefully, N predeposition was followed under 900°C in POCl<sub>3</sub>/O<sub>2</sub> ambients for 10 minutes and in N<sub>2</sub> gas for 10 minutes sequentially. N<sup>+</sup> oxidation and drivein were performed with 925°C, O2 ambient for These P-/N+ double diffusion 30 minutes.

(h) Alloy/passivation

Fig. 3. Processing steps for VDMOS.

processes are key steps to control the channel length, threshold voltage stability, and P<sup>+</sup>/P<sup>-</sup> junction depth. The difference in lateral diffusion between the P and N regions forms a controllable 1 to 2 µm channel length along the surface. The sequential diffusion processes made the final vertical junction depth of P<sup>+</sup>, P<sup>-</sup> and N<sup>+</sup> as 6.5  $\mu$ m, 4  $\mu$ m and 2.5  $\mu$ m, respectively. After depositing 6000Å thickness of SiO<sub>2</sub> which has 8% phosphorus concentration, PSG flowing was performed at 925°C, H<sub>2</sub>/O<sub>2</sub> ambient (Fig. 3-(e)). The PSG film and underlying N<sup>+</sup> oxide were etched out carefully. For reducing N<sup>+</sup> source to metal contact resistance, plug doping process was carried at 1000°C with POCl<sub>3</sub>/O<sub>2</sub> ambient (Fig. 3-(f)). After etching the plug and P<sup>+</sup> oxide successively, 2% Si-Al alloy was sputtered for the gate and source electrodes (Fig. 3-(g)). Silicon nitride film was deposited by PECVD as passivation layer (Fig. 3-(h)). For back side (drain) metallization, Cu-Zn alloy was used.

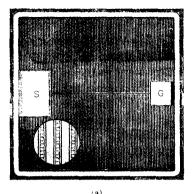

A surface photomicrograph of the completed device structure is shown in Fig. 4-(a). A cross section of the device after angle lapping and junction delineation is shown in Fig. 4-(b). Gate and source pad area were 680  $\mu$ m x 720  $\mu$ m and 900  $\mu$ m x 1280  $\mu$ m respectively. The chip area including guard ring was 4800  $\mu$ m x 4840  $\mu$ m, and was assembled in T0-220 and T0-3 package.

#### III. Results and discussions

#### 1. Breakdown and on-resistance characteristics

Resistivity and thickness of the epi-layer was measured by C-V plot method and film thickness gauge (FTG), respectively. The breakdown voltage and on-resistance characteristics of this device were compared with the values expected from (3), (4) and (5) (Table 1). The active area (A) excluding guard rings and bonding pads is  $16.4 \text{ mm}^2$ . The well junction depth (W<sub>j</sub>), well width (s) and well spacing (a) are  $6.5 \mu \text{m}$ , 29  $\mu \text{m}$  and  $13 \mu \text{m}$  respectively.

As shown in table 1, on resistances of devices have about  $2 \sim 3$  times higher than theoretical values. The reasons for this differences may come from the unstabilities of fabrication

Fig. 4. (a) Photograph of the VDMOS power transistor.

(b)

(b) Photograph of device cross section delineated by angle lapping and junction staining techniques.

Table 1. Comparision of some experimental breakdown and on-resistance characteristics with expected value.

| T <sub>e</sub> p <sub>i</sub> *1<br>(μm) | $ ho_{ m e}{ m p}_i \ (\Omega-{ m cm})$ | BV<br>(V) | R <sub>on</sub><br>(Ω) | $R_{e}p_{i}^{*}{}_{2}$ $(\Omega)$ | R,*2<br>(Ω) | $R_{on}^{*2}$ $(\Omega)$ |

|------------------------------------------|-----------------------------------------|-----------|------------------------|-----------------------------------|-------------|--------------------------|

| 27. 6                                    | 19                                      | 380       | 1. 9                   | 0.37                              | 0.24        | 0,61                     |

| 27.7                                     | 14                                      | 380       | 1.3                    | 0. 27                             | 0. 18       | 0.45                     |

| 29.3                                     | 14                                      | 380       | 1.4                    | 0.29                              | 0.18        | 0.47                     |

| 27.2                                     | 15                                      | 380       | 1.5                    | 0.28                              | 0. 19       | 0.47                     |

| 32. 2                                    | 12                                      | 430       | 1. 1                   | 0.29                              | 0. 15       | 0.44                     |

| 25. 0                                    | 6                                       | 310       | 0.5                    | 0.10                              | 0.08        | 0, 18                    |

<sup>\* 1 :</sup> T<sub>0</sub>p<sub>1</sub> = W + W

process such as the epitaxial layer growth, P double diffusion, and so on.

<sup>\* 2 :</sup> Expected value from (3), (4) and (5)

#### 2. Guard Ring Effect on Breakdown Voltage

In Fig. 5, the breakdown voltage of the guard ring structure has shown to be a relatively sensitive function of the seperation between the main junction and the guard ring. Guard ring spaces were varied from  $10 \mu m$  to  $80 \mu m$  with  $0.010 \sim 0.015 \Omega$ -cm of substrate resistivities.

Fig. 5. Breakdown voltage vs guard ring space.

For this substrate,  $3 \times 10^{14} \text{ cm}^{-2}$  and  $6 \times 10^{14} \text{ cm}^{-2}$  of boron were implanted with 100 KeV energy. In fact, these guard rings are made at  $P^+$  diffusion process. Within the ranges of implant dose and sheet resistance, the optimum guard ring space was  $20 \, \mu \text{m}$ . Compared with no guard ring function, the guard ring structure having  $20 \, \mu \text{m}$  space showed the improvement of about 30 to 40 percent in breakdown voltage. Using this result, three guard rings were adapted in main chip. The space distances between junctions were  $20 \, \mu \text{m}$ ,  $20 \, \mu \text{m}$  and  $24 \, \mu \text{m}$ , respectively.

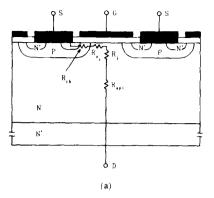

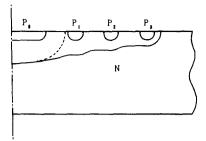

The reason of multi guard ring is illustrated in Fig. 6 [1].

The depletion layer is initially associated with the main junction  $P_0$ , and extends outward with increasing reverse bias. The spacing between  $P_0$  and  $P_1$  is such that punch through occurs before the avalanche breakdown voltage of the cylindrical junction associated with  $P_0$ . Thus the maximum electric field across the main junction  $P_0$  is limited, any further increase in reverse voltage is taken up by  $P_1$  until

Fig. 6. Diffused field-limiting ring.

the depletion layer punches through to  $P_2$ , and so on. Ultimately, the device breakdown at cylindrical junction is associated with the last diffused ring. To avoid excessively large chip area, practical number was limited to three guard rings. A test chip which has 200 times reduced active area with a combination of three guard rings and metal equipotential ring is shown in Fig. 7. Metal equipotential ring was set for the improvement of the device reliability.

Fig. 7. A full photograph of reduced test chip with three guard rings and metal equipotential ring.

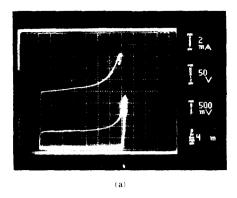

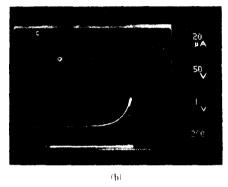

Fig. 8-(a) and (b) show the breakdown characteristics of the test chip. Compared with no-guard-ring device (Fig. 8-(a)), three-guard-ring device (Fig. 8-(b)) has 30 percent increase of breakdown voltage. As shown in Fig. 8-(b), 430 V of breakdown voltage could be obtained.

### 3. Main Chip Characteristics

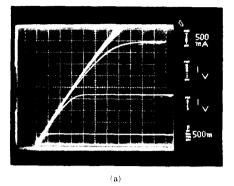

Fig. 9-(a) and (b) show the linear and

Fig. 8. Breakdown characteristics of test chip;

- (a) no-guardring.

- (b) combination of three-guard-rings and metal equipotential ring.

saturation characteristics of main chip.

From Fig. 9-(a), it can be seen that on-resitance  $(R_{cn})$  is 1.1  $\Omega$ . The threshold voltage  $V_{gs(th)}$  is defined as the gate-source bias required for a drain-source current of 1 mA. The summary of the power MOSFET parameters was listed in Table 2.

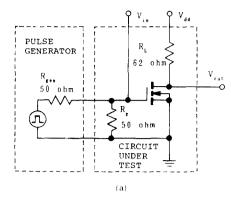

Shown in Fig. 10 is the switching test circuit and response of the device in a T0-220 package. With a 10 V, 200  $\mu$ s pulse applied to the plate, the characteristics shown in Fig. 9-(b) are measured at the output. Turn-on delay, rise, turn-off delay and fall time were 60 ns, 40 ns, 100 ns, respectively.

#### IV. Conclusion

The design, fabrication, and device measure-

Fig. 9. (a) Linear.

(b) Saturation characteristics of main chip.

Table 2. VDMOS electrical data and test conditions.

Code; PM07 # 09. Package; TO - 220

| ELECTRICAL CHARACTERISTICS |             |      |                                                                      |  |  |  |

|----------------------------|-------------|------|----------------------------------------------------------------------|--|--|--|

| Parameter                  | Measurement | Unit | Test Conditions                                                      |  |  |  |

| $BV_{dss}$                 | 410~440     | V    | $V_{gs}=0$ , $I_d=ImA$                                               |  |  |  |

| V <sub>es</sub> (th)       | 4.0~4.2     | V    | $V_{gs} = V_{ds_1} I_d = 1mA$                                        |  |  |  |

| R es (on)                  | 1.0~1.2     | ohm  | $V_{gs} = 10V$ , $I_d = 2.5A$ , pulse test                           |  |  |  |

| I₂ (on)                    | > 5         | A    | $V_{gs} = 10V, V_{ds} = 10V$                                         |  |  |  |

| g(fs)                      | 3.0         | A/V  | $V_{ds} = 10V$ , $I_d = 2.0A$ , pulse test                           |  |  |  |

| Cin                        | 2000        | pf   | $V_{gs} = 0$ , $V_{ds} = 25V$ , $f = 1 MHz$                          |  |  |  |

| t <sub>a</sub> (on)        | 60          | ns   | V <sub>dd</sub> = 200V                                               |  |  |  |

| t <sub>r</sub> (rise)      | 40          | ns   | V <sub>gs</sub> = 0 to 10V pulse test<br>  (200 us, 0.5% duty cycle) |  |  |  |

| t <sub>d</sub> (of f)      | 100         | ns   | R <sub>1</sub> = 620hm , R <sub>gen</sub> = 50 ohm                   |  |  |  |

| t, (fall)                  | 50          | ns   | I <sub>d</sub> about 3 A                                             |  |  |  |

ments for a high voltage vertical double diffused MOSFET have been discussed. The process was that  $N^-/N^+$  epitaxial wafer was used as the

Fig. 10. Illustration of the dynamic switching capability of the VDMOS transistor

(a) Test circuit.

(b) Output response.

starting material and  $P^-/N^+$  double diffusion was involved, simultaneously forming  $P^+$  guard rings around the chip. Using these techniques and  $12~\Omega-cm$ ,  $32~\mu m$  thick  $N^-$  epi-layer, drain breakdown voltage as high as 430 V, onresistance as low as  $1.1~\Omega$  and current capability more than 5 A were achieved within an area of  $4800~\mu m$  x  $4840~\mu m$ .

#### References

[1] S.K. Ghandhi, Semiconductor Power Devices - Physics of Operation and Fabrica-

- tion Technology. Wiley New York, pp. 34-90, 141-261, 1977.

- [2] S.M. Sze, Physics of Semiconductor Devices, 2nd ed., Wiley New York, pp. 169-174, 1981.

- [3] B.J. Baliga, et al., "The evolution of power device technology", IEEE Trans. Electron Devices, vol. ED-31, pp. 1570-1591, Nov. 1984.

- [4] E. Fong, et al., "Power DMOS for high-frequency and switching applications", *IEEE Trans. Electron Devices*, vol. ED-27, pp. 322-330, Feb. 1980.

- [5] B.J. Baliga, "A power junction gate fieldeffect transistor structure with high blocking gain", IEEE Trans. Electron Devices, vol. ED-27, pp. 368-373, Feb. 1980.

- [6] J.D. Meindl, et al., "A high voltage MOS switch", IEEE J. Solid-State Circuits, vol. SC-10, pp. 136-146, June 1975.

- [7] J.D. Meindl, et al., "An experimental and theoretical analysis of double-diffused MOS transistors", IEEE J. Solid-State Circuits, vol. SC-10, pp. 322-331, Oct. 1975.

- [8] C.A.T. Salama, et al., "Nonplanar power field-effect transistor", IEEE Trans. Electron Devices, vol. ED-25, pp. 1222-1228, Oct. 1978.

- [9] J.D. Plummer, et al., "Modeling of the onresistance of LDMOS, VDMOS and VMOS power transistors", *IEEE Trans. Electron Devices*, vol. ED-27, pp. 356-367, Feb. 1980.

- [10] C. Hu, et al., "Optimum design of power MOSFET's", IEEE Trans. Electron Devices, vol. ED-31, pp. 1693-1700, Dec. 1984.

- [11] M.S. Adler, et al., "Theory and breakdown voltage for planar devices with a single field limiting ring", *IEEE Trans. Electron Devices*, vol. ED-24, pp. 107-113, Feb. 1977.