# 고효율 및 고전력밀도 3-레벨 PFC 컨버터

양정우, 지상근\*, 강정일\*\*, 한상규<sup>†</sup> 국민대학교 POESLA, Solu-M\*, ㈜삼성전자\*\*

# High Efficiency and High Power Density 3-Level Power Factor Correction Converter

Jung woo Yang, Sang Keun Ji\*, Jeong il Kang\*\*, Sang Kyoo Han<sup>†</sup> Kookmin University POESLA, Solu-M\*, SAMSUNG Co Ltd\*\*

#### **ABSTRACT**

본 논문은 고효율 및 고전력밀도 3 레벨 PFC(Power Factor Correction) 컨버터를 제안한다. 기존 PFC의 고 전력밀도를 위한 스위칭 주파수 상승은 스위칭 특성이 우수한 소자를 적용하거나, 별도의 스너버 회로가 요구되므로 설계가 복잡하며 고전력밀도 달성에 한계가 있다. 제안 PFC 컨버터는 3 레벨 방식을 적용하여 각 스위칭 소자의 전압 스트레스를 절반으로 감소시켰으며, 스위치 손실 저감을 통한 고속 스위칭 동작으로리액티브 소자의 고밀도화를 달성하였다. 또한, 기존의 3 레벨 방식은 디지털 제어를 통해 스위칭 소자의 전압 평형이 이루어졌지만[1], 본 논문에서는 아날로그 IC에 전압 평형을 위한 RC Delay 회로와 소수의 SMD(Surface mount devices) 소자만을이용하여 별도의 제어회로 없이 전압 평형이 가능하므로 고전력밀도 달성에 유리하다. 제안회로의 타당성을 검증하기 위해 CRM(Critical conduction mode) PFC 컨버터를 기반으로 250W급 시작품 제작을 통한 실험 결과를 제시한다.

# 1. 서 론

최근 초소형 및 초고밀도 전원장치가 제품의 핵심기술로서 새롭게 부상하고 있는 추세에 있다. 전력변환 컨버터의 스위칭 주파수 상향을 통해 큰 부피를 차지하는 리액티브 소자의 소형 화가 가능하지만, 스위칭 주파수 상승에 따른 스위칭 손실 증가로 스위치의 심각한 손실과 발열을 발생시킨다. 스위칭 소자의 전압 스트레스는 스위치 양단 전압에 의해 결정되므로 전압 첨두치를 낮춰 전압과 전류가 중첩되는 크기와 시간을 줄임으로써 스위칭 손실을 저감하고 이를 통한 스위칭 주파수 상승으로 인덕터의 사이즈 저감이 가능하다. 본 논문에서는 2개의 스위치를 직렬연결 함으로써 전압 첨두치를 반으로 줄여 스위칭 손실을 저감하고, 아날로그 제어와 SMD소자만을 이용하여모든 스위칭 소자의 전압평형이 가능한 고효율 및 고전력밀도 3 레벨 PFC 컨버터를 제안한다.

## 2. 제안 3-레벨 PFC 컨버터

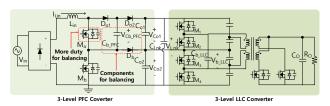

그림 1은 제안 3 레벨 PFC 컨버터와 3 레벨 LLC 컨버터를 나타낸다. 제안 컨버터는 스위칭 소자의 전압 스트레스 저감을 위해 스위치  $M_aM_b$  및 다이오드  $D_{ol},D_{o2}$ 가 직렬 연결되어 있으며, 전압평형을 위해  $M_a$ 는  $T_{delay}$ 후,  $M_b$  보다 늦게 턴 오프 동작이 이루어진다. 각 스위칭 소자의 전압 평형을 위한 전압 평형 커패시터인  $C_{b\_PFC}$ , 링크 전압 평형을 위한  $C_{ol},C_{o2}$ 와 전압 평형 다이오드  $D_b$ 로 구성된다.

그림 1 제안 3-레벨 PFC 컨버터

Fig. 1 A proposed 3-Level PFC Converter

#### 2.1.1 제안 3-레벨 PFC 컨버터의 전압 평형 원리

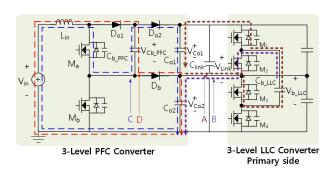

그림 2는 제안 3 레벨 컨버터의 각 전압 평형 커페시터  $C_{\rm ol}$ ,  $C_{\rm o2}$  및  $C_{\rm b.PFC}$ 의 전압 평형 원리를 나타내며 설명의 편의를 위해, 3 레벨 LLC는 1차 측만 나타낸다. 제안된 3 레벨 PFC 컨버터의 링크 커페시터  $C_{\rm ol}$ ,  $C_{\rm o2}$ 는 제안 PFC 컨버터의 출력에 연결되는 3 레벨 LLC 컨버터를 이용하여 전압평형 보장이 가능하다. [2] 3 레벨 LLC 컨버터는  $M_{\rm l.}M_{\rm l.}$ 와  $M_{\rm l.}M_{\rm l.}$  스위치가 각각 동시에 구동된다.  $M_{\rm l.}M_{\rm l.}$ 가 턴 온시, 그림 2의 'A'와 같은 경로로 도통하여  $V_{\rm b.LLC}$  =  $V_{\rm col}$  =  $V_{\rm link}/2$ 가 된다. 반대로  $M_{\rm l.}M_{\rm l.}$ 가 턴 온 시, 그림 2의 'B'와 같은 경로로 도통하여  $V_{\rm b.LLC}$  =  $V_{\rm col}$  =  $V_{\rm link}/2$ 가 된다. 상기 동작으로 식 (1)이 성립하게 된다.

$$V_{Co1} = V_{Co2} = V_{b\ LLC} = V_{link}/2 \tag{1}$$

그림 2의 'C'는 전압 평형 커패시터의 전압( $V_{\text{Cb,PFC}}$ )이 링크 전압의 절반보다 큰 경우를 나타낸다. 그림 2와 같이 전압 평형 커패시터의 전압이 링크커패시터  $C_{02}$ 전압보다 크면, 다이오 드  $D_{02}$ 는 도통하며, 전압 평형 커패시터는 방전되어  $V_{\text{Cb,PFC}}$  =  $V_{\text{Co2}}$  =  $V_{\text{link}}$ /2가 된다. 이 때, 전압 평형 커패시터의 방전을 위해서  $M_a$ 는  $M_b$ 보다 더 늦게 턴 오프 동작이 이루어진다.

그림 2 제안 컨버터의 전압 평형 원리

Fig. 2 A principle of voltage balancing for the proposed converter

그림 3 제안 3-레벨 컨버터의 전압 클램핑 경로

Fig. 3 Voltage clamping direction of the proposed 3-level PFC converter

반대로 그림2의 'D'는 전압 평형 커패시터의 전압이 링크 전압의 절반보다 작은 경우를 나타낸다. 그림 2과 같이 전압 평형 커패시터의 전압이 링크 커패시터  $C_{ol}$ 의 전압보다 작게되면, 다이오드  $D_{o2}$ 는 도통하지 않고 다이오드  $D_{b}$ 가 도통하게된다. 이를 통해 전압 평형 커패시터는 충전되며,  $V_{Cb\_PFC}$  =  $V_{Col}$  =  $V_{link}/2$ 가된다.

$$V_{\textit{Cb\_PFC}} = V_{\textit{Co1}} = V_{\textit{Co2}} = V_{\textit{link}}/2 \tag{2}$$

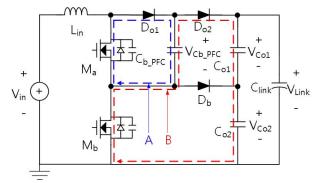

#### 2.1.2 제안 3-레벨 PFC 컨버터의 전압 클램핑 경로

그림 3은 스위치 및 다이오드의 양단 전압이 클램프 되는 경로를 나타내었다. 스위치  $M_b$ 와  $D_{c2}$ 는 그림 3의 'A'에 나타낸 경로와 같이 서로 반대로 동작하여 전압 평형 커패시터에 의해 링크전압의 절반으로 클램프 된다. 또한, 스위치  $M_a$ 와  $D_{c1}$ 은 그림 3의 'B'에 나타낸 경로를 통해 링크전압의 절반으로 클램 프 되므로 모든 스위치 및 다이오드의 전압 첨두치를 링크 전압의 절반으로 보장할 수 있다.

## 2.2 스위치 손실비교 및 설계가이드 2.2.1 스위치 손실 비교

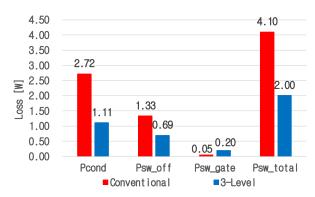

표 1은 동일한 패키지를 가지는 스위치의 주요 사양을 나타낸다. 제안 컨버터는 링크전압의 절반으로 스위치의 양단 전압이 클램핑 되므로, 낮은 내압을 가지는 고사양의 스위치 적용이 가능하다. 그림 4는 두 스위치에 대해 동작방식은 CRM, 입력전압= $90~V_{rms}$ , 출력전압=390~V, 스위칭 주파수= $250^\circ330~kHz$ 조건에 대해 제안 컨버터와 기존 부스트 PFC 컨버터의 스위칭손실을 비교하였다. 제안 컨버터 및 기존 컨버터는 ZVS(Zero~Voltage~Switching)에 의해 턴 온 손실 및 드레인 소스 커패시터에 의한 손실은 없으므로 도통손실( $P_{cond}$ ), 턴 오프 손실  $(P_{sw\_off})$  및 게이트 드라이버 손실( $P_{sw\_gate}$ )을 나타내었다.

표 1 스위치 주요 사양 Table 1 Specification of power switch

| Parameters         | IPB600N25N3 | IPB60R380P6 |

|--------------------|-------------|-------------|

| Package            | TO 263      | TO 263      |

| Maximum voltage    | 250 [V]     | 600 [V]     |

| Maximum current    | 18 [A]      | 10.6 [A]    |

| On resistance      | 90 [mΩ]     | 440 [mΩ]    |

| Output capacitance | 150 [pF]    | 42 [pF]     |

| Gate charge total  | 22 [nC]     | 19 [nC]     |

그림 4 기존 PFC 컨버터와 제안 3-레벨 PFC 컨버터의 스위 치 손실 비교

Fig. 4 Switch loss comparison between the conventional PFC converter and the proposed 3-level

제안 컨버터의 경우, 두 개의 스위치를 직렬로 연결하므로 기존 PFC 대비 2배의 턴 온 저항을 가지므로 동일한 사양의 스위치를 적용하는 경우, 도통 손실이 2배가 된다. 하지만, 낮은 스위치 전압 스트레스로 인해 낮은 턴 온 저항을 가지는 우수한 성능의 스위치 적용이 가능하므로 2개의 스위치를 직렬 연결하더라도 기존 대비 약 49% 수준으로 도통손실을 저감할 수 있다. 또한, 낮은 전압 스트레스로 인해 기존 대비 턴 오프손실을 약 51% 수준으로 저감이 가능하다. 따라서 기존 컨버터 대비 약 50%의 스위칭 손실 저감이 가능하다.

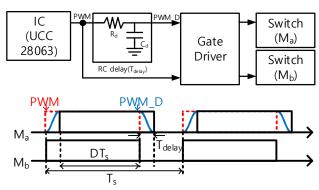

#### 2.2.2 RC 시정수

그림 5는 제안 컨버터의 전압 평형을 위한 스위칭 방식에 대한 블록 다이어그램 및 각 스위치의 게이트 소스 전압을 나타낸다. 앞서 2.1에 나타낸 바와 같이 제안 컨버터의 구동 원리에서 전압 평형 커패시터 전압  $V_{Cb,PFC}$ 가 링크전압의 절반보다큰 경우, 전압 평형 커패시터의 방전을 위해  $M_a$ 스위치는  $M_b$ 스위치보다 긴 턴 온 시간이 요구된다. 이를 위해,  $M_a$ 스위치의 PWM(Pulse Width Modulation)신호는 RC delay 회로를 거쳐 RC시정수만큼 지연된 신호를 통해 스위칭을 하게 된다. 지연된 신호에 의해  $M_a/M_b$ 가 서로 동시에 턴 온 되는 구간이 전력단의 시비율이 되므로 지연된 신호의 2배에 해당하는 시비율 손실 구간이 발생하므로 식 3에 나타낸 바와 같이 최대 입력전 압조건에서 요구되는 턴 온 시간의 2배보다 작아야한다.

$$T_{delay} = 2\pi R_d C_d < \frac{T_s}{2} (1 - \frac{V_{in\_peak}}{V_o})[s]$$

(3)

그림 5 제안 컨버터의 스위칭 방식

Fig. 5 A switching method of the proposed converter

#### 2.2.3 전압 평형 커패시터

전압 평형 커패시터  $C_4$ 의 경우, 2.2.1의  $T_{delay}$  시간동안 입력인덕터  $L_{in}$ 와 공진을 한다.  $M_a$ 스위치가 턴 온 되어있는 동안, 전압을 일정하게 유지해 주기 위해서는 입력 인덕터와 전압 평형 커패시터의 공진 주기는 식 4와 같이  $T_{delay}$ 보다 매우 커야한다.

$$T_{delay} \ll 2\pi \sqrt{L_{in}C_{b\_PFC}}[s]$$

(4)

또한,  $M_b$  스위치 턴 오프시 전압을 유지할 만큼 충분히 커야 하므로, 식 5와 같이 스위치의 드레인 소스 커패시턴스보다 매우 큰 값을 가져야한다.

$$C_{ds} \ll C_{b\_PFC}$$

(5)

#### 3. 제안 3-레벨 PFC 컨버터 실험 결과

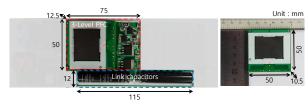

제안된 3 레벨 PFC 컨버터의 우수성과 이론적 분석의 타당성을 검증하기 위해 그림 6과 같이 시작품을 제작하여 실험결과를 제시한다. 제안 컨버터의 IC는 TI UCC28063을 사용하였으며, 동작모드는 CRM이다. 사용된 파라미터 및 설계 사양을표1 에 정리하였다.

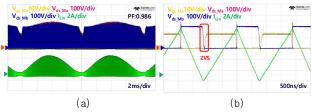

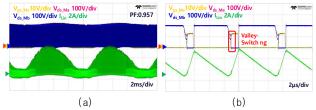

그림 7(a), 7(b)는 입력전압 115V<sub>ms</sub> 그림 8(a), 8(b)는 230V<sub>ms</sub>에서의 정상상태 주요파형으로 각 그림의 (a)는 주요소자인 스위치 M<sub>a</sub> 게이트 소스 전압과 M<sub>a</sub>M<sub>b</sub>의 드레인 소스전압 및 L<sub>n</sub> 전류에 대해 60Hz 한 주기 동안의 파형을 나타내며, (b)는 주요 소자의 세부 파형을 나타낸다. 그림 7(a)와 그림 8(a)의 측정된 입력 역률은 115V<sub>ms</sub>입력에서 0.986, 230V<sub>ms</sub> 입력에서 0.957로 우수한 성능을 확인하였다.

그림 7(b)와 그림 8(b)의 세부파형에 나타낸 바와 같이 입력전압  $115V_{ms}$ 에서는  $ZVS(Zero\ Voltage\ Switching)$ , 입력전압  $230V_{rms}$ 에서는 및  $VS(Valley\ Switching)$ 이 이루어짐을 확인할 수 있다. 또한,  $M_a$ 와  $M_b$  스위치의 드레인 소스 양단전압은 서로 같은 값을 가지며, 이는 전압 평형에 의해서 링크전압의 절반인 195V임을 확인할 수 있다.

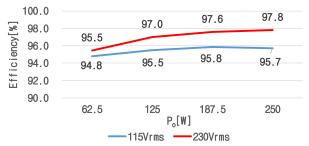

제안회로의 효율은 그림 9과 같이 부하 187.5W, 입력 115V<sub>rms</sub>에서 95.8%를 보이고 있으며, 전부하 250W, 입력 230Vrms에서 최대 97.8%를 보이고 있다. 이론적 분석과 실험 결과로부터 제안회로의 우수성과 각 부 소자 설계가 타당함을 알 수 있다.

표 2 주요 사양 Table 2 Specifications

| Parameters           | Value                        | Parameters          | Value     |

|----------------------|------------------------------|---------------------|-----------|

| $V_{\text{in}}$      | 90 ~ 264 [V <sub>rms</sub> ] | Lin                 | 43.2 [μH] |

| $V_{\text{nonimal}}$ | 115 & 230 [V <sub>ms</sub> ] | C <sub>b</sub>      | 100 [nF]  |

| $V_{o}$              | 390 [V]                      | $C_{o1}$ , $C_{o2}$ | 47 [nF]   |

| Po                   | 250 [W]                      | $C_{Link}$          | 164 [µF]  |

| $f_{\rm sw}$         | 230~550[kHz]                 | $T_{delay}$         | 33 [nsec] |

그림 6 제안 3-level PFC 시작품 및 인덕터

Fig. 6 The proposed 3-level PFC Converter and inductor

그림 7 제안 3-레벨 PFC 컨버터의 정상상태 주요파형(115V<sub>rms</sub>) Fig. 7 Key waveform of the proposed 3-level PFC converter under the steady state(115V<sub>rms</sub>)

그림 8 제안 3-레벨 PFC 컨버터의 정상상태 주요파형(230V<sub>rms</sub>) Fig. 8 Key waveform of the proposed 3-level PFC converter under the steady state(230V<sub>rms</sub>)

그림 9 제안 3-레벨 PFC 컨버터의 부하별 효율

Fig. 9 Efficiency of the proposed 3-level PFC converter according to load condition

# 4. 결론

본 논문에서는 고효율 및 고전력밀도 3 레벨 PFC 컨버터를 제안하였다. 제안회로는 2개 스위치의 직렬연결 및 제안 구동 방식을 통해 스위치의 전압 스트레스를 저감시킴으로써, 스위칭 손실을 저감하였으며, 별도의 부가회로 없이 아날로그 제어와 SMID타입의 소자만으로 모든 스위칭 소자의 전압 평형을이루었다. 제안회로의 타당성 검증을 위해 250W급 시작품 제작을 통해 우수한 성능 및 설계의 타당성을 확인하였다.

본 논문은 (주)Solu M 연구지원과 2018년 국민대학교 교내 연구비 지원에 의하여 연구되었음

### 참 고 문 헌

- [1] Y. Tang, D. Zhu, C. Jin, P. Wang and F. Blaabjerg, "A Three Level Quasi Two Stage Single Phase PFC Converter with Flexible Output Voltage and Improved Conversion Efficiency," in IEEE Transactions on Power Electronics, vol. 30, no. 2, pp. 717 726, Feb. 2015.

- [2] Hyun Su Gu, Hyo Hoon Kim, Sang Keun Ji, Dong kyun Ryu, Heung Gyoon Choi, Sang Kyoo Han "High Efficiency and High Power Density 3 Level LLC Resonant Converter", Power Electronics Annual Conference, pp. 182 183. July. 2017