## **Optimum Channel Thickness of Nanowire-FET**

고형우, 김종수, 김신근, 신형철 Inter-University Semiconductor Research Center (ISRC) and School of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-747, Korea E-mail: hwkogo@snu.ac.kr

Nanowire-FET은 Gate-All-Around (GAA) 구조로 차세대 반도체 소자 구조로 여겨지고 있다. Nanowire-FET은 채널 두께에 따라  $I_D$ - $V_G$  curve에 매우 중요한 영향을 끼친다. 따라서본 논문은, Edison 시뮬레이션을 이용하여 Nanowire-FET의 Silicon Thickness에 따른 여러특성을 비교하여 최적 Silicon Thickness에 대해 연구하였다.

#### I. Introductuion

반도체 소자가 세대를 거듭할수록 scale down 됨에 따라 Short Channel Effect (SCE)과 같은 예기치 못한 현상들이 발생하였다. 이에, 반도체 소자는 일반적인 MOSFET 구조에서 FinFET과 같은 Multi-gate 구조로 바꾸면서 이러한 예기치 못한 현상들에 의한 영향을 줄이며, 최근 14 nm 노드의 트랜지스터까지 계속된 발전을 해왔다. 그러나 10 nm 아래의 node로 갈수록 양자 효과에 의한 여러현상들이 나타나게 된다. 이에 따라 게이트제어능력이 우수한 Gate-All-Around(GAA) 소자인 Nanowire-FET이 10 nm 이하의 차세대의 반도체시장을 이끌 유력한 후보로 대두되고 있다. Nanowire-FET은 채널의 두께에 따라 양자 효과에기인한 여러 현상들이 나타난다. 따라서, 본 논문은 양자 효과를 고려하여 Nanowire-FET의 최적 channel 두께에 대한 연구를 진행하였다. 시뮬레이션을 이용하여 Nanowire-FET의 채널 두께별 소자 특성을 분석하였으며, 얻어진 분석 결과는 향후 미래 소자 구조를 제안하는데 도움을 줄 수 있다.

### II. Device Structure and Simulation Setup

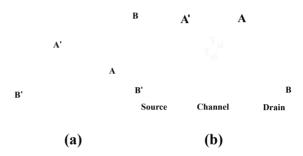

Nanowire-FET의 두께별 특성을 확인하기 위하여 시뮬레이션에 사용된 소자는 Fig. 1. 에 도식화하였다. Fig. 1. (a)는 소자의 전체적인 모습이고 Fig. 1. (b)는 사용된 소자의 단면도이다. 소자는 ITRS (International Technology Roadmap for Semiconductors)의 5nm 노드의 기준에 맞게 설계되었다. 채널은 p-type으로 도핑되었고, 채널 길이는 12.2 nm로 설정되었다. 본 논문에서는 Edison Simulation을 이용하여 채널의 Silicon 두께( $T_{si}$ )를 3 nm ~ 7 nm 로 나누어 각각의  $I_D$ - $V_G$ 를 추출하였고, 각각의 두께에 해당되는  $V_T$  variation, DIBL, SS, Conductivity 및 Current Density 특성을 분석하였다.

#### III. Results and Discussion

시뮬레이션을 이용하여 channel의 silicon 두께 (T<sub>si</sub>)별로 Nanowire-FET의 I<sub>D</sub>-V<sub>G</sub>를 Fig. 2. 에 도식화하였다. 채널 두께(T<sub>si</sub>)가 감소할수록 전류 성분 또한 감소하는 경향을 볼 수 있는데, 이는 Multi-gate 소자 구조에서 채널 두께가 10 nm 이하로 내려감에 따라 발생되는 Quantum effect로 설명될 수 있다. GAA 구조의 Nanowire-FET은 V<sub>G</sub>가 증가함에 따라 Fig. 1. 의 좌표에서 y와 z방향에 대해 electron들이 confinement가 생기게 되고,

Fig. 1. Nanowire-FET 소자 구조

Fig. 2. 두께별 I<sub>D</sub>-V<sub>G</sub> Curve

Fig. 4. SS 특성 및 DIBL 특성

오직 x 축에 대해 자유로운 one-Dimensional Electron Gas (1DEG) 가 발생한다. 이러한 현상은 Silicon Channel에서 전자들의 분포에 대해 energy subband의 형성을 초래하여, electron들이 존재할 수 있는 DOS (Density Of States)가 나뉘어지는 현상을 초래한다. Silicon Thickness(Tsi)가 얇아질수록 Conduction Band 에서의 mimum subband의 에너지 준위는 증가하게 된다.[1] 이에 따라  $T_{si}$ 가 줄어들수록  $V_{7}$ 는 증가하게 되고  $I_{on}$ 은 감소하는 경향을 Table. 1. 과 Fig. 1. 에서 확인할 수 있다. 1DEG는 inversion layer가 oxide

# Silicon Thickness

Fig. 3. Current Density 및 Mobility 비교

Fig. 5. Conductivity 및 On Current Density 비교

$T_{si}$ 7 nm 2 nm 3 nm 4 nm 5 nm 6 nm  $V_{T}[V]$ 0.8285 0.5404 0.4774 0.447 0.4294 0.4177  $I_{on}/I_{off}$ 7.44x108 1.1x109 6.95x108 4.32x108 4.1x108 1.68x108

$V_{DS} = 0.75 \text{ V}$

Table 1. V<sub>T</sub> 및 I<sub>on</sub>/I<sub>off</sub> Ratio

surface 부근에서 국한되는 것이 아닌 silicon-film 의 두께에 대한 Volume inversion을 발생한다. T<sub>si</sub> 가 줄어들수록 inversion 되는 electron은 channel 의 중심으로 모여지게되고, electron concentration 의 peak점 또한 Si-SiO<sub>2</sub> 계면에서 점차 channel의 중심으로 이동하게 된다.[2] 이에 따라 T<sub>si</sub>가 줄어들수록, mobile carrier의 peak concentration은 Si-SiO<sub>2</sub> interface에서 멀어지므로 surface scattering의 영향이 줄어들게 되고, 따라서 electron의 mobility가 증가하는 경향이 존재한다.[3] 그러나 T<sub>si</sub>가 10 nm 이하의 부근에서는 Volume inversion이 일어나더라도 Si-SiO<sub>2</sub> interface까지 물리적으로 가까워지기 때문에 Surface scattering의 성분을 무시할 수 없게 된다. 이에 따라, V<sub>G</sub>가 V<sub>T</sub> 이상의 전압 조건에서 T<sub>si</sub>가 10 nm 이하로 점차 줄어들수록 surface scattering에 의해 모빌리티가 감소하는 것을 Fig. 3. 에서 확인할 수 있다.[3] 또한, 3 nm 이하에서 전자의 모빌리티가 급격하게 감소하는 경향은 Si-SiO<sub>2</sub> interface roughness에 의해 발생되는 potential fluctuation 으로 인한 thickness fluctuation scattering 으로 설명될 수 있다.[4] 즉, T<sub>si</sub>가 10 nm 아래의 영역에서 T<sub>si</sub>가 줄어들수록 Volume inversion으로 인한 mobility는 감소하는 경향과, Conduction band에서의 Energy band split으로 V<sub>T</sub>는 증가하는 경향이 존재한다. 따라서 on-current가 실리콘 두께가 줄어들수록 감소하는 경향을 보인다. 그러나, GAA구조의 FET에서 T<sub>si</sub>가 줄어들게 되면 channel에 대해 Gate control 능력이 향상되므로, 이런 점을 고려하여 Nanowire-FET에서 T<sub>si</sub>에 대한 최적 포인트를 찾는 것이 고찰되어야 한다. 이러한 관점에서 Fig. 4. 에서 T<sub>si</sub>에 대한 최적 포인트를 찾는 것이 고찰되어야 한다. 이러한 관점에서 Fig. 4. 에서 T<sub>si</sub>에 대한 Subthreshold Swing과 DIBL(Drain Induced-Barrier Lowering) 을 도식화하였다. T<sub>si</sub>가 줄어들수록 channel에 대한 Gate의 control 능력을 나타내는 지표인 식 (1)의 Natural Length는 감소한다. 소한다.

(1)

이에 따 라 DIBL 역시 T<sub>si</sub>가 줄어들수록 줄어들게 되고, SS 또한 60 mV/decade에 근접하는 것을 Fig. 4. 에서 확인할수 있다. T<sub>si</sub>가 2 nm인 소자가 DIBL 측면에서 가장 우수한 성능을 보이나, electron mobility와 density의 곱으로 표현되는 conductivity 관점에서 최적 두께는 3 nm 인 것을 Fig. 5. 에서 확인할수 있다. 또한, Fig. 5. 에서 On Current를 단면적으로 나눈 결과 최적의 Current Density를 갖는 Silicon Thickness는 3nm 인 것을 확인하였다. 즉, Gate의 컨트롤 능력을 나타내는 SS, DIBL과 Conductivity의 trade-off을 고려할 경우 2 nm 소자보다 3 nm 소자가 적절하다고 볼 수 있다. 또한, Table. 1. 에서 T<sub>si</sub>가 3 nm 소자가 가장 높은 I<sub>on</sub>/I<sub>off</sub> Ratio를 갖으므로 Steep Switching에 우수한 소자라고 볼 수 있다.

#### IV. Conclusion

본 논문에서는 Nanowire-FET의 최적 Silicon Thickness에 대해  $I_D$ - $V_G$  Curve를 이용하여  $V_T$ , Carrier Mobility, DIBL 및 SS 특성을 분석하였다. Silicon Thickness 가 줄어들수록 Carrier Mobility는 감소하고,  $V_T$  또한 증가하므로 current가 감소하는 것을 확인하였다. 또한, 이와는 대조적으로 두께가 줄어들수록 channel에 대한 Gate Control능력을 나타내는 DIBL과 SS 모두 향상되는 것을확인하였다. 그러므로 이러한 상반되는 두 가지관점에서, Current에 직접적으로 관여하는 Conductivity와 On-Current Density를 모두 고려할경우에  $T_{si}$ 가 3 nm 소자가 이상적인 SS와 DIBL과

높은  $I_{on}/I_{off}$  ratio를 갖는 것을 확인하였다. 따라서, 차세대 반도체 소자로 쓰일 Nanowire-FET은 Silicon 두께가 3 nm 로 설계되어야한다.

#### V. ACKNOWLEDGEMENT

This research was supported by the Brain Korea 21 Plus Project in 2015, Synopsis and the EDISON Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT & Future Planning (2012M3C1A6035302).

VI. References

[1] J.P. Colinge, J. C. Alderman, W. Xiong: Quantum-Mechanical Effects in Trigate SOI MOSFETs. IEEE Transactions on Electron Devices 53-5, 1131 (2006)

Devices 53-5, 1131 (2006)

[2] B. Majkusiak, T. Janik, and J. Walczak: Semiconductor Thickness Effects in the Double-Gate SOI MOSFET. IEEE Transactions on Electron Devices 45-5, 1127 (1998)

[3] G. Tsutsui, M. Saitoh, T. Saraya, T. Nagumo, T. Hiramoto: Mobility onbancoment disease.

[3] G. Tsutsui, M. Saitoh, T. Saraya, T. Nagumo, T. Hiramoto: Mobility enhancement due to volume inversion in [110]-oriented ultra-thin body double-gate nMOSFETs with body thickness less than 5 nm. Technical Digest of IEDM 729 (2005)

IEDM, 729 (2005)

[4] Ken Uchida and Shin-ichi Takagi: Carrier scattering induced by thickness fluctuation of silicon-on-insulator film in ultara thin-body Metal-oxide-semiconductorfield-effect transistor. Appl.Phys. Lett 82. 2916(2003)