#### d-q 좌표 변환 기법을 이용한 단상 계통 연계형 전력변환기의 PLL 오차 보상기법

<u>박창석</u>\*, 감승한\*, 정태욱<sup>†</sup> 경남대학교\*,<sup>†</sup>

# Single-Phase Grid-Connected Power Converter of the PLL Error Compensation Method Using d-q Coordinate Transformation

Chang-Seok Park\*, Seung-Han Kam\*, Tae-Uk Jung† Kyungnam University\*.†

Abstract - 단상 계통 연계형 전력 변환기에서 계통과 연계하기 위해서는 계통의 위상 정보를 정확히 측정하여 전력 변환기의 출력 주파수와 위상이 동일한 상태로 전류가 공급 되도록 해야 한다. 본 논문에서는 단상 d-q 좌표 변환 기법을 통한 위상 동기화 기법을 적용하여 왜곡된 계통전압이 d축 전압에 야기 되는 에러 성분을 최소화 하는 보상 기법을 제안한다. 제안된 기법은 동기 d축 전압을 일정한 주기로 적분하여에러 성분을 최소화 한 후, PI제어를 통해 d축 전압을 0으로 수렴하게하는 기법이다. 제안된 기법은 추가적인 하드웨어를 요구하지 않는다.본 논문의 타당성을 검증하기 위해 3[kW]급 단상 계통 연계형 전력변환기 시작품을 제작하고 실험을 통해 증명하였다.

#### 1. 서 톤

신흥개발도상국가의 발달 및 삶의 질 향상으로 인하여 에너지 수요는 세계적으로 급증하고 있으나, 기존 석유, 석탄 등의 화석연료의 고갈, 지구 온난화와 같은 환경적 문제로 인하여 전 세계 에너지 포트폴리오의 급격한 변화가 이루어지고 있다. 그러므로 신재생 에너지를 원활이 사용하기 위해 전력변화기는 필수적이다.

단상 계통 연계형 전력변환기는 산업 및 가전용으로 사용되는 태양광, 풍력, 그리고 연료전지 등의 신재생 에너지 전력변환 시스템으로 매우 중요하다. 단상 계통 연계형 전력변환기에서 Phase-Locked-Loop(PLL)는 전력품질, 시스템의 안정성과 효율을 결정짓는 중요한 요소이다. PLL은 계통의 전압을 측정하여 계통의 위상과 전력변환기 출력전압의 위상을 일치 시키는 기법으로, 계통 전압의 정확한 측정이 필요하다. 하지만, 왜곡된 계통 전압은 계통의 위상 정보에 오차를 발생시키기 때문에 왜곡된 계통 전압으로 인해 발생하는 오차를 보상하는 기법이 반드시 필요하다.

본 논문에서는 d-q 좌표 변환 기법을 이용하는 PLL의 오차를 보상하기 위해 적분기를 추가한 PLL 오차 보상 기법을 제안한다.

#### 2. 본 론

#### 2.1 위상 검출 PLL 기법

일반적으로, 단상 계통 연계형 전력변환기의 계통 위상정보는 계통 전압의 Zero-crossing-points(ZCP)를 검출하여 알 수 있다. ZCP 검출 기법은 정현과 형태의 계통 전압을 측정하고, 아날로그 Op-amp를 통하여 구형과 형태의 신호로 변환 뒤 Rising edge 와 Falling edge 신호를 측정하여 위상정보를 검출하는 기법이다. 이 기법은 빠른 응답 특성과 간단한 알고리듬을 가지는 이점이 있다. 하지만, ZCP 검출 기법은 전력용 반도체 소자의 스위청에 의해 야기된 과도 상태에는 둔감한 단점이 있다.

d-q 좌표 변환 기법은 계통 전압을 측정하여 디지털 전역통과필터 (APF)를 통과시켜 위상이 90°도 지연된 가상 전압을 생성하고, 직류 성분의 d축 전압과 q축 전압을 생성하여 위상을 검출하는 기법이다. 이기법은 응답 특성이 ZCP 검출 기법에 비해 응답 특성이 늦고 다소 복잡한 알고리듬을 가지지만 아날로그 소자에서 발생하는 전력손실을 줄일 수 있고, 계통의 왜곡 상태에서도 견고하다.

본 논문에서는 계통 전압의 위상정보를 검출하기 위해서 d-q 좌표 변환 법을 이용하였다.

#### 2.2 단상 d-q 좌표 변환 시스템 모델링

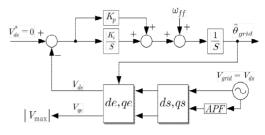

그림 1은 d-q 좌표 변환 기법을 이용한 단상 계통 연계형 전력변환기의 PLL 제어 알고리듬을 나타내고 있다. PLL 시스템은 그림 1에서 나타내듯이 계통 전압을 디지털 APF로 통과시켜 위상이 90도 지연된 가상 전압을 생성하여 좌표 변환을 하게 된다. 측정된 계통 전압  $V_{grid}$ 을  $V_{ds}$ 로, APF에 통과된 가상 전압을  $V_{qs}$ 로 두고, d-q 좌표 변환 기법을 이용하여  $V_{de}$ ,  $V_{ae}$ 로 변환한다.

〈그림 1〉 PLL 제어 기법의 블록선도

이상적인 계통 전압  $V_{ds}$ 와 디지털 APF에 통과된  $V_{qs}$ 는 다음 식 1과 같이 계산할 수 있다.

$$\begin{split} V_{ds} &= -V_m \sin \omega_g t \\ V_{qs} &= V_m \cos \omega_q t \end{split} \tag{1}$$

여기서,  $V_m$ 은 계통의 전압 최댓값,  $\omega_a$ 는 계통 각 주파수이다.

PLL 출력 값  $\hat{\theta_g}$ 를 추종하기 위해서는 좌표 변환 행렬  $T(\hat{\theta_g})$ 를 이용하여 계산 할 수 있다.

$$T(\hat{\theta}_g) = \begin{bmatrix} \cos \hat{\theta}_g & \sin \hat{\theta}_g \\ -\sin \hat{\theta}_g & \cos \hat{\theta}_g \end{bmatrix}$$

(2)

식 (2)를 고려하여  $V_{ds}$ 는 다음 식 (3)과 같이 나타낼 수 있다.

$$V_{ds} = -V_m \sin(\theta_a - \hat{\theta}_a) \tag{3}$$

계통 위상각  $\theta_g$ 와 추종각  $\hat{\theta}_g$ 의 차이인 에러 값  $\Delta\theta$  값이 매우 작다면 계통 위상각을 추종 할 수 있다. 그러나 실제  $V_{ds}$ 는 고조파 성분과 잡음 등을 포함하고 있어 다음 식 (4)와 같이 계산할 수 있다.

$$V_{ds\ err} = -V_m \sin \omega_a t + \Delta_{err} \tag{4}$$

식 (2), (4)를 이용하여 동기 d, q축 전압  $V_{de}, V_{qe}$ 는 다음과 같이 나타 낼 수 있다.

$$\begin{bmatrix} V_{de\_err} \\ V_{qe\_err} \end{bmatrix} = \begin{bmatrix} V_{ds\_err} \\ V_{qs\_err} \end{bmatrix} \begin{bmatrix} \cos \hat{\theta}_g & \sin \hat{\theta}_g \\ -\sin \hat{\theta}_g & \cos \hat{\theta}_g \end{bmatrix}$$

(5)

식 (5)와 같이, 실제 계통 전압에 존재하는  $\Delta_{err}$ 로 인해  $\Delta\theta$ 는 존재하게 된다. 따라서 추종각은 계통과 일치되지 않아 오차 보상기가 필요하다.

### 2.3 제안된 적분기 PLL 오차 보상 기법

제안된 기법은 동기 d축 전압을 적분하여  $\Delta_{err}$ 값을 계산한 뒤 제거하는 기법이다. 적분 값  $\Delta_{err1}$ 과  $\Delta_{err2}$ 는 0에서  $\pi$ 까지,  $\pi$ 에서  $2\pi$ 까지 각 각 두주기로 나누어 적분을 하였고, 식 (5)로부터  $V_{ds.err}$ 는 Sine, Cosine의 함수로 구성되어 있는 것을 알 수 있다. 동기 d축 전압을  $\Delta_{err1}$ ,  $\Delta_{err2}$ 로 나누어 각 각 적분하게 되면 Cosine 함수는 자동적으로 제거되어진다. 따라서 다음 식 (6), (7)과 같이 계산할 수 있다.

$$\begin{split} \Delta_{err1} &= \int_{0}^{\pi} V_{ds\_err} d\hat{\theta}_{g} \\ &= \int_{0}^{\pi} (\Delta_{err} \cos \hat{\theta}_{g} + \Delta_{err} \sin \hat{\theta}_{g} = 2\Delta_{err} \\ \Delta_{err2} &= \int_{\pi}^{2\pi} V_{qs\_err} d\hat{\theta}_{g} \\ &= \int_{\pi}^{2\pi} (\Delta_{err} \cos \hat{\theta}_{g} + \Delta_{err} \sin \hat{\theta}_{g} = -2\Delta_{err} \end{split} \tag{6}$$

$$\Delta_{err}total = 2\Delta_{err} + (-2\Delta_{err}) = 0 \tag{7}$$

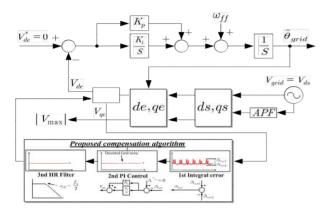

그림 2는 제안한 알고리듬을 포함한 PLL 블록 선도이다.

〈그림 2〉 제안된 PLL 오차 보상 기법의 블록선도

## 3. 실험 결과

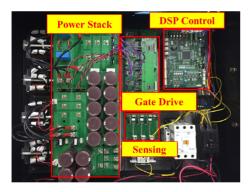

〈그림 3〉 3[kW] 단상 계통 연계형 전력변환기 시작품

제안된 알고리듬을 검증하기 위해 3[kW]급 단상 계통 연계형 전력변환기를 통해 실험 하였다. 제작된 시작품 프로세서는 DSP28335를 사용하였으며, 10[kHz]의 인터럽트 주파수로 동작된다. 시작품의 정수 파라메타는 다음 표 1과 같다.

〈표 1〉 시스템 파라메타

| Input voltage             | [Vdc]  | 200-400 |

|---------------------------|--------|---------|

| Output voltage            | [Vrms] | 220     |

| Rated power               | [kW]   | 3       |

| DC-DC switching frequency | [kHz]  | 20      |

| DC-AC switching frequency | [kHz]  | 16.5    |

| Filter inductor           | [mH]   | 2       |

| DC_Link Cap.              | [mF]   | 1.7     |

| Rated efficiency          | [%]    | 92      |

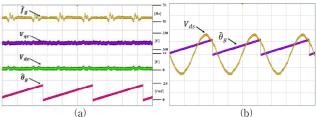

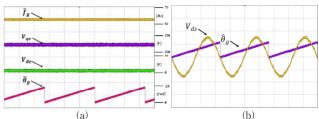

그림 4는  $\Delta_{err}$ 가 존재하는 실험 결과를 제시한다. 그림 4(a)와 같이, 동기  $\mathrm{d}$ -q축 전압  $V_{de}$ ,  $V_{qe}$  와 추정 주파수  $\hat{f}_g$ 는 왜곡된 파형을 보인다. 또한 그림 4(b)에서 보듯이 계통 전압과 추정각  $\hat{\theta}_g$ 의 위상은 일치하지 않는다.

〈그림 4〉 제안된 기법을 적용하지 않은 PLL 결과 값

그림 5는  $\Delta_{err}$ 를 고려하여 제안된 오차 보상 기법을 적용한 실험 결과이다. 동기  $\mathrm{d}$ -q축 전압 $V_{de}$ ,  $V_{qe}$  와 추정 주파수  $\hat{f}_g$ 는 왜곡된 파형이 제거되고 정상적으로 추종 되는 결과를 알 수 있다. 또한 계통 전압과 추종각  $\hat{\theta}_a$ 의 위상은 일치한다.

<그림 5> 제안된 오차 보상 기법이 적용된 PLL 결과 값

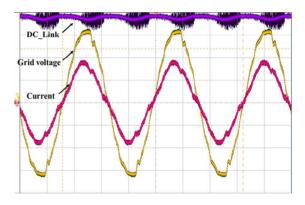

그림 6은 3[kW] 동작 중 시스템의 DC\_Link 전압, 계통과 연계된 출력 전압 그리고 출력 전류를 나타낸다. 이 때 역률은 0.99, 효율은 93[%]로 동기 d축 전압의 오차 보상 기법의 타당성을 증명하고 있다.

<그림 6> 3[kW] 동작 중 출력 특성

### 3. 결 론

본 논문에서는 d-q 좌표 변환 법을 이용하는 PLL의 오차 보상 기법을 제안한다. 동기 d축 전압에 발생하는 오차 값을 적분기의 추가를 통해 감소 시켜 계통 전압의 위상에 정확하게 추종하였다. 제안된 알고리듬은 별도의 추가적인 하드웨어 없이 구성할 수 있으며, 알고리듬은 여러 실험을 통해 검증하였다. 제안된 기법은 유사한 입·출력 사양을 갖는 여러 응용분야에서 유용하게 사용될 수 있을 것으로 사료된다.

#### **감사의 글** 이 논문은 2013년도 정부(교육부)의 재원으로 한국연구재단의 기초연구사업 지원을 받아 수행된 것임(NRF-2013R1A1A2010691)

## [참 고 문 헌]

- [1] S. J. Lee, J. K. Kim, and S. K. Sul, "A new phase detecting method for power conversion systems considering distorted conditions in power system," in IEEE Ind. Appl. Conf. (IAS), vol. 4, pp. 2167–2172. 1999.

- [2] L.G.B. Rolim, M. Aredes, "A DQ Synchronous Reference Frame Current Control for Single-Phase Converters," Power Electronics Specialists Conference, pp. 1377–1381, 2005.