# 로드보상 알고리즘을 적용한 고효율 정류기 설계

<u>서기봉</u>\*, 김윤성\*<sup>†</sup>, 박귀철\* 동아일렉콤 전원연구소\*

# Design of high efficiency rectifier with load compensation algorithm

Ki-Bong Seo\*, Yun-Sung Kim\*†, Gwi-Chul Park\* Dongahelecomm R&D Center\*

Abstract - 본 논문에서는 고성능 통신용 전원 장치의 고밀도 설계 시발생되는 과도부하 출력전압 특성 저하 현상을 개선하기 위해 DC-link 커패시터를 추가하지 않고 PFC 부와 DC-DC 부의 제어부 통신을 활용한 로드보상 알고리즘을 적용하여 성능을 개선한다. 제안된 설계 방식은  $34.45W/m^3$ 의 전력밀도, 3kW 출력 용량의 프로토타입을 통해 96% 이상의 효율 특성 및 2% 이하의 과도 출력전압 특성을 확인한다.

#### 1. 서 론

고성능 전원 장치의 연구는 다양한 응용분야에서 활발히 진행되고 있 다. 특히 통신용 전원 장치는 고효율 특성, 높은 출력전압 안정도 및 박 형 타입의 고밀도 성능을 요구한다. 또한 절연 설계, 높은 역률, 낮은 노 이즈 특성은 실장 및 부품기술 그리고 회로기술 연구의 선도적 역할을 하고 있다. 따라서 고성능 통신용 전원 장치는 대부분 고 역률 및 출력 노이즈 저감을 위해 PFC (power factor corrector) 부와 DC-DC 부로 구성된 2-스테이지 구조 이며 DC-DC 부는 절연형 회로방식으로 설계 된다. 이때 PFC 부는 0.99 이상의 역률 및 97% 이상의 효율 성능을 만 족하기 위해 boost 타입의 회로 방식이 연구 개발되어 왔다. 특히 종래 boost PFC 회로의 브릿지 다이오드의 전도 손실을 개선시킨 SBL PFC (semi-bridgeless boost PFC)는 고용량 설계 및 박형, 고밀도, 고효율 설계에 적합하다 [1]. 한편 DC-DC 부의 경우 수백 와트 이상의 절연형 설계에서는 브릿지 타입 회로 선정이 타당하며 특히 고속 스위칭 손실 을 최소화하기 위해 개발된 PSFB (phase shift full bridge), LLC, SRC 회로 방식이 높은 효율 성능을 기대 할 수 있다. 최근 LLC 최적화 연구 는 96~97% 이상의 효율 성능을 나타내고 있다 [2].

반면 이러한 고밀도, 고효율 회로방식을 적용하더라도 각 스테이지를 연계하는 DC-link 커패시터 설계는 출력 용량과 비례하게 되며 고속 스위칭 및 회로방식 변경으로는 전체적인 사이즈 저감 효과에 한계가 있다. 따라서 고밀도 설계에서는 holdup time을 위한 최소 DC-link 커패시터 설계를 적용해야 높은 밀도의 실장 설계가 가능하다. 그러나 이러한 경우 출력 과도부하 조건에서 출력 전압 품질이 떨어지는 문제가 발생된다. 본 논문에서는 holdup time을 위한 최소 커패시터 설계 조건을 유지하면서 제어 알고리즘을 통한 출력 전압 안정화 보상을 위한 로드보상 제어 알고리즘을 적용한 사례를 분석하여 보고 하였다.

## 2. 본 론

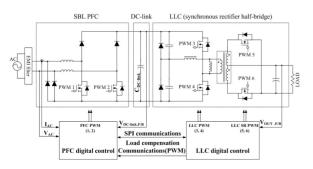

그림 1은 본 논문에서 제안한 로드보상 제어 알고리즘이 적용된 3kW급 정류기의 기본 회로도 이며, PFC 부는 SBL, DC-DC 부는 LLC로구성된다. 이때 각 스테이지는 DSP를 통해 별도로 제어되고 있으며 원활한 제어를 위하여 고속 통신이 가능한 SPI 통신을 통해 제어 신호를전달하며, 로드보상 알고리즘은 실시간 정보전달이 가능한 별도의PWM 통신으로 구성하였다.

〈그림 1〉 3kW급 2-스테이지 정류기 기본 회로 (SBL+LLC)

한편 SBL은 입력전압, 입력전류, 출력전압 정보를 기본 계측하며 각입력 라인과 연결된 2개의 FET를 제어하기 위해 2개의 PWM을 사용하고 있다. LLC는 출력전압 계측 및 효율성능 향상을 위해 2차 측 출력 정류부를 FET 동기 정류방식으로 구성하여 총 4개의 PWM으로 구성한다. 로드보상 알고리즘은 DC-DC 부의 출력 부하 정보를 PFC 제어기에 전달하기 위한 통신을 하며, 기타 외부 통신은 CAN을 사용한다. 각 스테이지는 DC-link 커패시터를 통해 연결되며, 일반적인 커패시터 설계는 출력 용량에 따라 설계되어 왔다 [3]. 반면 전체 실장 부품 중 자성소자와 커패시터의 사이즈가 가장 크기 때문에 커패시터의 비 최적화설계는 고밀도 실장 설계를 어렵게 한다. 따라서 최근 고밀도 실장 설계 사례에서는 시스템의 최소 holdup time 만을 고려하여 커패시터를 최소설계하는 추세이다.

### 2.1 정류기 DC-link 커패시터 설계

본 연구에서는 holdup time 만을 고려한 최소 설계를 적용하였고, 시스템에서 요구사양을 기준으로 정류기 출력전력  $1.5 \mathrm{kW}$ 에서 교류 입력전압이  $20 \mathrm{ms}$  동안 off 되었을 때 정류기 출력전압이  $43 \mathrm{V}_{DC}$  이상 유지되도록 설계 하였다. 이때 LLC의 DC 이득을 만족할 수 있는 DC-link 전압은  $355 \mathrm{V}_{DC}$  이상이 필요하며, 최소 DC-link 전압 값은 식(1) 과 같다. Holdup time을 만족하기 위해 필요한 DC-link 커패시터의 최소용량은약  $973 \mathrm{uF}$ 으로 식(2)로 계산되며, 최종 선정된 DC-link 커패시터는  $270 \mathrm{uF}$ , 4개를 병렬로 설계하였다. 설계된 커패시터 용량은 식(3)과 같이PFC 출력  $3 \mathrm{kW}$ 에서  $120 \mathrm{Hz}$ 의 저주과 리플 전압  $27 \mathrm{VZ}$ 로 계산된다.

$$V_{\scriptscriptstyle DC-link} = \frac{N \cdot V_{\scriptscriptstyle OUT}}{M} \tag{1}$$

$$C_{DC-link.holdup} = \frac{2 \cdot P_{OUT} \cdot T_{holdup}}{\eta_{DC-DC} \cdot (V_{DC-link.nom}^2 - V_{DC-link.holdup}^2)}$$

(2)

$$\Delta V_{DC-link.holdup} = \frac{2 \cdot P_{OUT}}{2 \cdot 120 \, Hz \cdot V_{DC-link.nom} \cdot C_{DC-link.holdup}} \tag{3}$$

# 2.2 과도부하 출력전압 특성 개선

LLC 회로방식은 입력 전압에 대한 DC 이득의 범위가 넓지 않으며, 최소 설계된 DC-link 커패시터의 부족한 용량으로 출력 과도부하 시 출력 전압의 변동이 크게 발생된다. 또한 120Hz, 27V의 저주파 리플은 PFC를 안정적으로 제어하는데 문제를 발생 시킬 수 있으므로, DC-link 전압을 feedback 받는 계측부에 LPF (low pass filter) 등을 고려하여 설계되어야 한다.

### 2.2.1 LLC DC 이득 특성

커패시턴스 영역에서 동작하는 LLC는 공진 주파수 보다 낮은 스위청 주파수로 동작할수록 DC 이득의 기울기가 급격히 증가하는 특성을 갖는다. 따라서 DC-link의 큰 전압 변동이 발생 될 때 LLC를 낮은 스위청 주파수로 동작하면 높은 DC 이득으로 출력 전압을 안정적으로 유지할 수 있다. 낮은 스위칭 주파수를 사용하여 DC 이득을 높이기 위해서는 공진 탱크 및 LLC 동작에 대한 검토가 필요하다. 일반적으로 공진용으로 재작된 커패시터라 하더라도 스위칭 주파수에 따라 허용 전류 내량이 감소하는 특징을 가지고 있다. 100kHz를 기준으로 높은 주파수 구간에서는 최대 허용 전류 내량을 보장하지만 낮은 주파수 구간에서는 허용 전류 내량이 급격히 감소하는 특성을 가지고 있다. 따라서 충분한 공진 커패시턴스의 전류 내량을 만족하기 위하여 공진 커패시터 용량을 수 있다. 그러나 전류 내량을 만족하기 위하여 공진 커패시터 용량을 증가하면 초기 기동, 출력 단락 등의 동작 조건에서 안정성에 문제가 발생될 수 있다.

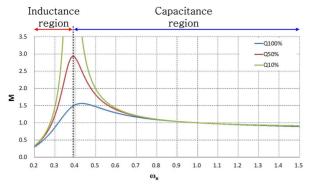

〈그림 2〉 LLC의 DC 이득곡선

또한 보다 큰 DC 이득을 확보하기 위하여 두 번째 공진 주파수보다 낮은 스위칭 주파수를 사용하면 인덕턴스 영역으로 동작하여 DC 이득 특성의 기울기가 바뀌어 정상적인 제어가 불가능하다. 따라서 LLC의 DC 이득을 높여 과도부하 시 출력 품질을 개선하는 것은 공진 탱크 및 회로방식 특성의 한계로 인해 적용하기 어렵다.

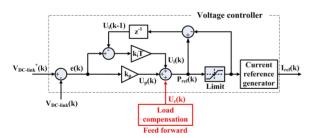

## 2.2.2 로드보상 알고리즘

전술한 바와 같이 높은 LLC의 DC 이득 및 DC-link 커패시터 용량 확 보 등은 출력 과도부하 시 출력전압 품질 문제를 해결하기 어렵다. 따라 서 출력 과도부하가 발생 되었을 때 부하의 변동 정보를 PFC 제어기에 feed forward 방식으로 보상 할 수 있는 로드보상 알고리즘을 적용한다. 그림 3은 일반적으로 사용되는 PFC 전압 제어기에 로드보상 알고리즘 을 추가한 제어 블록도 이다. 기존의 일반적인 PFC 제어기는 과도부하 시 전압의 변동이 발생된 후의 계측 값  $V_{DC-link}(k)$ 로 DC-link 전압을 제 어하기 때문에 부족한 용량의 DC-link 커패시터에 의한 전압 변동을 보 상하기 어렵다. 한편 전압 계측에 사용된 LPF는 응답속도를 제한하는 요소로 작용할 수 있다. 반면 로드보상 알고리즘은 출력 과도부하 정보 를 DC-link 전압의 변동이 발생되기 전에 실시간으로 출력 부하 변동 보상값  $U_c(k)$ 를 기존의 PFC 전압제어기 출력  $P_{ref}(k)$ 에 보상하므로 DC-link 전압의 변동을 효과적으로 개선할 수 있다. 또한 정상 상태에 서는 기존의 일반적인 전압제어기와 동일하게 제어되므로 DC-link 커패 시터 용량 부족 또는 과도부하에서 빠른 응답이 요구될 비교적 복잡하 지 않은 제어 알고리즘을 추하가여 효과적으로 특성을 개선 할 수 있다. 식(4)은 일반적인 PFC 전압제어기를, 식(5)는 로드보상 알고리즘이 적용 된 전압제어기 출력을 나타낸다.

$$P_{ref}(k) = U_{p}(k) + U_{i}(k) \tag{4}$$

$$P_{ref}(k) = U_{p}(k) + U_{i}(k) + U_{c}(k)$$

$$\tag{5}$$

<그림 3> 로드보상 알고리즘이 적용된 PFC 전압제어기 블록도

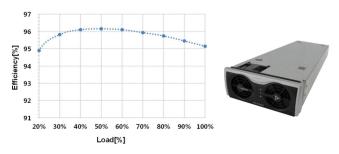

〈그림 4〉 정류기 효율 특성 및 제품 사진

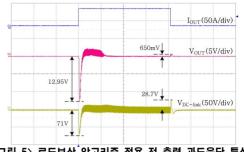

〈그림 5〉 로드보상 알고리즘 적용 전 출력 과도응답 특성

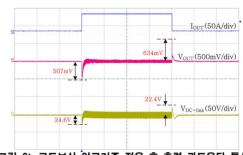

〈그림 6〉 로드보상 알고리즘 적용 후 출력 과도응답 특성

### 2.4 시험 결과

그림 4는 제안된 로드보상 알고리즘의 실효성을 검증하기 위해 제작된 3kW급 정류기의 외형 및 고효율 성능 결과이다. 제작된 프로토타입을 통해 로드 보상 전, 후의 개선 효과는 각각 그림 5와 그림 6을 통해 확

성능비교 시험은 최대출력의 10% 부하에서 100% 부하의 출력 과도부 하를 시험하였으며, 전압 제어기의 gain(ki, kp)은 동일한 조건으로 시험 하였다. 그림 5는 로드보상 알고리즘이 적용되지 않은 PFC 전압 제어기 로 시험한 결과로 출력 부하가 증가 할 때 DC-link 전압과 출력 전압의 변동은 각각 71V, 12.95V의 전압 강하 특성, 출력 부하가 감소할 때는 28.7V, 650mV의 전압 상승 특성을 확인하였다. 즉 출력 부하의 증가 시 전압 변동이 크게 발생되는 것을 확인 할 수 있으며, 부족한 DC-link 커패시터 용량으로 인해 발생되는 현상임을 알 수 있다. 그림 6은 로드보상 알고리즘 적용된 PFC 전압 제어기로 시험한 결과

이다. 출력 부하가 증가 할 때 DC-link 전압과 출력 전압의 변동은 각 각 24.6V, 507mV로 DC-link 전압은 약 46.4V, 출력 저압은 12.44V 과 도 저감 특성 효과를 확인하였다. 이때 최종 출력전압의 과도 출력전압 특성은 2% 이하 이다. 반면 출력 부하 감소 할 때는 로드보상 알고리즘 적용 전과 유사한 특성을 보였고 로드보상 알고리즘이 부족한 커패시터 의 보상 효과로 타당한 방식임을 알 수 있다.

# 3. 결

본 논문은 고밀도, 고효율 통신용 전원 장치 개발 시 소형 박형 설계를 위해 holdup time을 고려한 DC-Link 커패시터를 최소로 설계 하고 파 생되는 출력 전압 과도 문제를 로드 보상 제어 알고리즘으로 해결한 결 과를 보여 준다. 제안된 제어 보상 알고리즘은 추가 회로 없이 PFC 부 와 DC-DC 부 제어 회로 간 PWM 통신을 통해 구현이 가능하다. 성능 및 효용성을 검증하기 위해 34.45W/in³ (1U / 108.2 × 41.0 × 321.7 mm) 의 전력밀도, 출력전압 48V<sub>DC</sub>, 출력 용량 3kW급의 프로토타입을 통해 96% 이상의 효율 특성 및 2% 이하의 과도 출력전압 특성을 확인 하다

# [참 고 문 헌]

- [1] Yun-Sung Kim, Won-Yong Sung, Byoung-Kuk Lee, "Comparative Performance Analysis of High Density and Efficiency PFC Topologies," IEEE Trans. Power Electronics, vol. 29, no. 6, pp. 2666-2679, June 2014.

- [2] Yu, Ruiyang, Ho, Godwin Kwun Yuan, Pong, Bryan Man Hay, Ling, B.W.-K.,Lsm, J.,"Computer Aided Design and Optimization of High Efficiency LLC Series Resonant Converter," IEEE Trans. Power Electronics, vol. 27, no. 7, pp. 3243-3256, July 2012.

- [3] Raggi, K., Doerig, G., Biela, J., Kolar, J.W., "Comprehensive Design and Optimization of a High-Power-Density Single-Phase Boost PFC," IEEE Trans. Industrial Electronics, vol. 56, no. 7, pp. 2574-2587, July 2009.