# 독립 운전 모드 시 가상 캐패시터-저항 복합 임피던스를 이용한 인버터 병렬 운전 설계 및 분석

정교선<sup>\*</sup>,임경배<sup>\*</sup>, 최재호<sup>\*</sup> 충북대학교<sup>\*</sup>

# Design and analysis of the parallel inverters using virtual capacitive-resistive complex impedance in islanded mode

Kyosun Jung\*, Kyungbae Lim\*, Jaeho choi\*

Chungbuk National University\*

#### **ABSTRACT**

여러 가지 분산 발전 시스템들은 마이크로그리드의 형태를 지나고 있다. 이 마이크로그리드는 계통연계모드에서 부하의수요를 담당하게 되고, 계통 사고가 발생할 시 단독운전모드로 동작을 해야 한다. 드룹 제어 방식은 이 때 각각의 분산발전시스템에서의 유효전력과 무효전력 부하 sharing을 통해 안정적으로 전력을 공급 할 수 있고 순환 전류를 최소화 할 수 있다. 본 논문에서는 제안된 가상 저항과 캐패시터를 이용하여 인버터 병렬 운전 시스템을 위한 드룹 제어에 대해서 연구하였다. 그리고 가상 복합 임피던스에 따른 출력 임피던스에 대해서 연구하고 이에 따른 드룹 제어를 분석하여 PSIM 시뮬레이션으로 이를 검증하였다.

#### 1. 서 론

최근 계속해서 발생되는 화석 연료의 고갈로 인해 지구촌 환경 문제와 연료비용으로 인하여 친환경 에너지가 부각되고 있다. 에너지의 환경과 비용에 대한 관심이 증가하는 가운데, 분산 발전 시스템(DG)은 중앙 발전시스템과 비교하여 부하에 대한 지역적 접근성을 증대시키고 분산발전의 지역적 제어를 가능하게 하는 등 시스템의 유동적인 운용에 있어 큰 장점을 지닌다. 분산 발전 시스템은 태양광, 풍력 발전, 연료 전지 등으로 이루어져 있고 이러한 분산 발전 시스템들이 통합되어 하나의 마이크로그리드를 구성하게 된다.

마이크로그리드는 계통연계모드로 동작을 하다가 계통에 고 장이 발생할 시 독립운전모드로 전환하게 된다. 이러한 독립운 전모드에서 로컬 부하에 전력을 공급하게 되는데 이 분산발전 시스템들의 유효전력과 무효전력을 제어하기 위하여 드룹제어 방식이 쓰이게 된다.

본 논문에서는 가상 캐패시터를 포함한 인버터 병렬 운전에 대하여 좀 더 보완된 개선법을 적용 시키고 이에 따른 해석과 MATLAB과 PSIM 시뮬레이션을 통해 결과를 확인하였다.

# 2. 드룹 제어 및 시스템 모델링

# 2.1 개선된 RC 임피던스에 따른 출력 임피던스

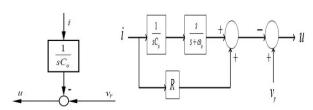

기존의 논문 [1],[2]에서는 그림 1처럼 인버터 출력 전류에 가상의 캐패시터를 추가하여 LC 직렬 공진으로 인해 인버터의 THD를 크게 개선하고자 하는 것이 목적이다. 하지만 이 같은 방식은 병렬 시스템의 임피던스 차에 의해서 DC 순환전류가

(a)가상 캐패시터 제어 블록도(b)개선된 임피던스 제어 블록도 그림 1 기존의 가상 임피던스과 개선된 임피던스 제어 블록도 Fig. 1 Existing virtual impedance and proposed impedance control block diagram

매우 커지게 된다. 그래서 본 논문에서는 그림 1처럼 기존의 C임피던스를 활용하여 하이패스필터와 저항을 이용하여 새로운 RC 임피던스를 제안하였다. 그림 1에서 i는 인버터 출력 전류,  $C_o$ 는 가상 캐패시턴스,  $v_r$ 는 전압 지령치,  $\omega_o$ 는 차단주파수, u는 가상 임피던스가 고려된 제어 신호를 뜻한다. 이 같은 두 개의 가상 임피던스 방식을 응용하여 출력 임피던스 전달함수를 구하고 보드선도를 통해 시스템을 해석해 볼 수 있다. 기존의 C임피던스와 제안된 RC 임피던스에 대한 출력 임피던스를 구하면 다음과 같다.

$$Z_{C}(s) = \frac{(sL + \frac{1}{sC_{o}}) \cdot \frac{1}{sC}}{(sL + sC_{o}) + \frac{1}{sC}} = \frac{s^{2}LC_{o} + 1}{s^{3}LCC_{o} + s(C_{0} + C)}$$

(1)

$$Z_{RC}(s) = \frac{(R + sL + \frac{1}{C_o(s + \omega_o)}) \cdot \frac{1}{sC}}{R + sL + \frac{1}{C_o(s + \omega_o)} + \frac{1}{sC}}$$

$$s^2 L C_o + s(LC\omega_o + C_oR) + C_o\omega_oR + 1$$

(2)

$= \frac{1}{s^3 C C_o L + s^2 (L C_o C \omega_o + C C_o R) + s (R C C_o \omega_o + C + C_o) + C_o \omega_o}$

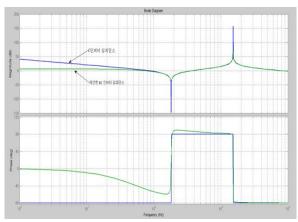

식 (1)은 C 임피던스에 대한 출력 임피던스를 뜻하고 식 (2)는 제안된 RC 임피던스에 대한 출력 임피던스를 말한다. 여기에서 L,C는 필터 인덕터와 캐패시터를 뜻한다. 이 두 개의 식을 이용한 보드선도가 그림 2에 표현되어있다. 이 것을 몇 가지 장점과 단점을 확인해 볼 수 있다.

- 장점 1)병렬 운전 하에서 임피던스 차에 의한 DC 순환전류 를 줄일 수 있다.

- 2)저항 성분과 하이패스필터를 통해 시스템 댐핑이 가능하다.

- 3)필터 캐패시터에 별도의 패시브 댐핑을 연결 할 필요가 없다.

그림 2 C와 RC 임피던스 출력 임피던스 보드선도 Fig. 2 C and RC output impedance bode diagram

단점 1)L인버터 보다는 낮지만 C 인버터에 비하여 THD 가 높아진다.

2)C인버터 보다 시스템이 복잡해진다.

#### 2.2 RC 출력 임피던스에 따른 드룹제어

본 논문에서는 출력 임피던스를 저항성과 동시에 캐피시턴스 성분을 가지고 있기 때문에 이에 따른 드룹제어식을 응용해야한다. 기존의 논문[3]에서는 기본 주파수에서의 위상을 45도로 맞추어 이에 따른 드룹제어식을 쓰고 있다. 본 논문에서도 45도로 맞추어 기본 주파수에서 R과 C의 영향이 동일하다는 가정하에 드룹제어식을 응용하였다.

$$\omega^* = \omega_{nom} + m(P+Q) \tag{3}$$

$$E^* = E_{nom} - n(P - Q) \tag{4}$$

식 (3)과 (4)에서  $\omega^*, E^*$ 은 시스템 지령 주파수와 전압이고  $\omega_{nom}, E_{nom}$ 은 정격 주파수와 전압이며 m,n은 주파수와 전압에 대한 드룹 계수이다. 그리고 P,Q는 각각 시스템 유효전력과 무효전력을 뜻한다.

# 3. 시뮬레이션

표 1 드룹제어 시뮬레이션 파라미터

Table 1 Parameters of droop control simulation

| DC link 전압  | 158V               | L,C 필터             | 0.55mH,20uF            |

|-------------|--------------------|--------------------|------------------------|

| 가상<br>캐패시턴스 | 2100uF             | 차단주파수 $(\omega_o)$ | 60Hz                   |

| 가상 저항       | 0.01Ω              | 드룹 계수 m            | $5 \times 10^{-5}$     |

| 드룹 계수 n     | $5 \times 10^{-7}$ | PCC 전압             | 380V(line to line RMS) |

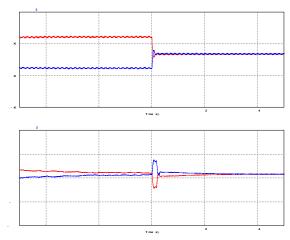

표 1은 제안된 RC 임피던스의 PSIM 시뮬레이션을 위한 파라미터이다. 본 논문에서는 표 1의 파라미터를 통해 시뮬레이션을 하였고 그 결과는 각각 그림 3과 그림 4와 같다. 그림 3에서는 제안된 RC 임피던스에서의 드룹제어를 응용한 두 인버터간의 유효전력과 무효전력 부하 분담을 보여준다. 0.5s에서드룹제어와 제안한 가상 임피던스를 적용하였다. 식(3)과 (4)에 대한 식이 전력 부하분담 적용효과를 보이는 것을 확인하였다.

그림 3 가상 캐패시터-저항을 포함한 드룹제어 시뮬레이션(유효전력(위),무효전력(아래)) Fig.3 Droop control simulation with virtual capacitor-resister(P(top),Q(bottom))

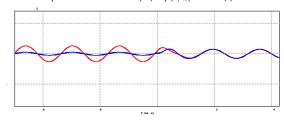

그림 4 제안된 임피던스 드룹제어에서의 출력전류 Fig.5 Droop control simulation with proposed impedance (output current)

그림 4는 제안된 임피던스 드룹제어의 두 인버터의 출력전류를 측정한 그림이다. 처음에는 임피던스 차에 의해 두 출력전류의 크기와 위상이 맞지 않지만 드룹제어 적용후에 전류는 동일해지고 이에 따라 순환전류의 크기는 크게 줄어든다.

# 4. 결론

본 논문에서는 기존의 가상 캐패시터를 이용한 기존의 논물을 응용하여 좀 더 보완된 가상 저항 캐패시터 임피던스를 해석해 보고 시뮬레이션을 통해 결과를 확인해 보았다. 이 같은 방식을 좀 더 보완하여 다양한 가상 임피던스 간을 직접 시뮬레이션하여 비교, 분석하면 각각의 장,단점을 응용 할 수 있을 것이다.

#### 참 고 문 헌

- [1] Q. C. Zhong, and Y. Zeng, "Can the output impedance of an inverter be designed capacitive?," in Conf. of Rec. IECON, pp. 1220 1225, 2011.

- [2] Q. C. Zhong, and Y. Zeng, "Control of inverters via a virtual capacitor to achieve capacitive output impedance" *IEEE Trans. on Power Electron.*, Vol. 29, No. 10, pp. 5568–5578, 2014.

- [3] W. Yao, M. Chen, J. Matas, J. M. Guerrero, and Z. M. Qian, "Design and analysis of the droop control method for parallel inverters considering the impact of the complex impedance on the power sharing," *IEEE Trans. on Ind. Electron.*, Vol. 58, No 2, 2011.