# 인터리브드 풀 브릿지 컨버터와 단상 하프 브릿지 인버터를 이용한 1.5kW급 PCS 설계

나광수\*, 나종국\*, 이희준\*, 신수철\*, 원충연\* 성균관대학교\*

# Design of 1.5kW PCS Using Interleaved Full-Bridge Converter and Single Phase Half-Bridge Inverter

Kwang Su Na\*, Jong Kuk Na\*, Hee Jun Lee\*, Soo Cheol Shin\*, Chung Yuen Won\*, Sungkyunkwan University\*

#### **ABSTRACT**

In this paper, a PCS which consists of high boost interleaved full bridge converter and single phase half bridge inverter is proposed. Proposed PCS is using two full bridge converter modules. PCS consists of parallel input / serial output. It can reduce turn ratio of high frequency transformer. In this paper, PCS which is using 1.5[kW] interleaved full bridge converter and single phase half bridge inverter is designed and verified stability of system through experiment.

# 1. 서 론

최근 환경오염, 화석연료의 고갈과 이로 인한 유가 상승 등의 원인으로 인해 신재생에너지원에 대한 관심이 높아지고 있다. 신재생에너지를 효율적으로 활용하기 위한 전력변환장치(PCS: Power Conditioning System)에 대한 연구 역시 활발하게 진행되고 있다.

주로 중·대전력용 PCS의 DC DC 컨버터로는 절연형 풀 브 릿지 컨버터를 많이 사용한다. 이때, 기존의 풀 브릿지 컨버터 는 출력측 다이오드의 전압 진동으로 소자에 큰 스트레스가 발 생하고, 높은 순환 전류로 인해 도통손실이 큰 단점이 있다.<sup>[1]</sup>

본 논문에서는 이러한 단점을 개선하기 위한 새로운 PCS를 제안하고, 실험을 통해 타당성을 검증하였다.

## 2. PCS 설계

## 2.1 기존 풀 브릿지 컨버터 문제점 개선

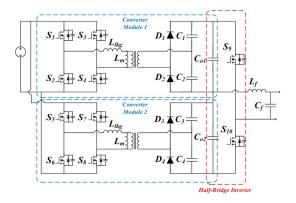

그림 1은 제안된 풀 브릿지 컨버터와 하프 브릿지 인버터의 결합회로를 나타낸다. 컨버터부는 풀 브릿지 컨버터로 구성하여 스위치와 다이오드의 전압 정격을 낮추었다. 그리고, 동일한 컨버터 모듈 2개를 병렬 입력 / 직렬 출력으로 구성하였다. 모듈의 인터리빙 제어를 통하여 컨버터 모듈의 입력 전류 리플을 낮추었다. 또한 전압 더블러 형태로 출력단을 직렬로 연결하여 변압기의 턴비를 줄여 무게와 가격을 줄였다.

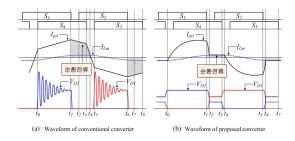

그림 2는 기존의 풀 브릿지 컨버터와 제안한 컨버터의 변압기의 1차측 전류와 다이오드 전압 파형을 나타낸다. 정류 커패시터로 다이오드의 전압을 일정하게 클램핑하고 소자 스트레스를 줄였다. 그리고, 출력단의 필터 인덕터를 제거하여 환류구간의 전류를 크게 줄여서 도통손실을 줄였다.

그림 1 제안된 시스템의 회로도 Fig. 1 Circuit diagram of the proposed system

그림 2 변압기 1차측 전류와 다이오드 전압 파형 비교 Fig. 2 Compare analysis of transformer current and diode voltage waveform

# 2.2 누설 인덕턴스 및 스위치 출력 커패시터 설계

제안된 컨버터에서 진상 레그 스위치와 지상 레그 스위치의 출력 커패시터들은 누설 및 자화 인덕턴스에 흐르는 전류에 의 해 충전 및 방전되어야 한다. 진상 레그 스위치의 출력 커패시 터를 충・방전 시키는 조건은 다음과 같다.

$$\frac{1}{2}L_{lkg}\dot{i}_{pri}^2 + \frac{1}{2}L_m\dot{i}_{L_m}^2 \ge \frac{1}{2}C_{oss}V_{in}^2 \tag{1}$$

지상 레그 스위치의 출력 커패시터를 충전 및 방전 시키는 조건은 자화 전류만이 영향을 미치기 때문에 다음과 같다.

$$\frac{1}{2}L_{m}i_{L_{m}}^{2} \ge \frac{1}{2}C_{oss}V_{in}^{2} \tag{2}$$

$L_{lkg}$ ,  $L_{m}$ ,  $i_{pri}$ ,  $i_{Lm}$ ,  $C_{oss}$ 는 각각 누설 인덕턴스, 자화 인덕턴스, 변압기 1차측 전류, 자화 인덕턴스 전류, 스위치의 출력 커패시턴스를 나타낸다.

# 2.3 전압 더블러 정류기 설계

제안한 컨버터는 전압 더블러 타입의 정류 커패시터와 변압 기 1차측의 누설 인덕턴스가 공진을 하도록 설계하였다. 공진 주파수  $f_r$ 을 스위청 주파수  $f_s$ 의 0.85배로 두고 다음의 식으로 공진 주파수를 계산하였다.

$$\omega_r = 2\pi f_r = \frac{n}{\sqrt{L_{lkq}C_r}} \tag{3}$$

따라서, 변압기 설계에 따라 턴비 n, 누설 인덕턴스  $L_{lkg}$ 를 결정하고 위 식을 다음 식처럼  $C_r$ 에 대해 정리하면 공진 커패시턴스를 구할 수 있다.

$$C_r = \frac{1}{L_{lkg}} \left(\frac{n}{2\pi f_r}\right)^2 \tag{4}$$

#### 3. 실험 결과

#### 3.1 시스템 설계

제안한 시스템 검증을 위하여 시스템을 구성하였다. 세트는 풀 브릿지 컨버터부와, 하프 브릿지 인버터부로 구성하였다.

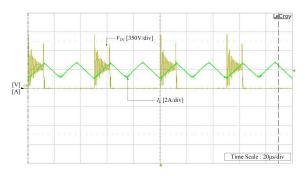

그림 3 기존 풀 브릿지 컨버터의 출력 다이오드의 전압과 인덕터 전류 파형

Fig. 3 Output diode voltage and Inductor current waveform of conventional full bridge converter

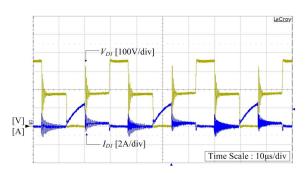

그림 4 제안한 풀 브릿지 컨버터 출력 다이오드의 전압과 전류 파형

Fig. 4 Output diode voltage and current of proposed full bridge converter

그림 3은 기존 풀 브릿지 컨버터의 출력 다이오드 전압과 전류 파형을 나타낸다. 다이오드 턴 오프시 전압 진동 현상이 발생하여 소자에 큰 스트레스가 발생한다. 전압 스트레스의 최 대치는 1100[V] 이상으로 출력 전압의 3배 이상 발생하였다.

그림 4는 제안된 풀 브릿지 컨버터의 출력 다이오드의 전압 과 전류 파형을 나타낸다. 전압 더블러 정류기를 이용하고 출 력단의 인덕터를 제거하였다. 이를 통해 환류 구간에서 전류의 크기를 줄여 도통손실을 저감하였다. 또한, 다이오드에 걸리는 전압이 정류 커패시터에 의해 출력전압으로 클램핑된다.

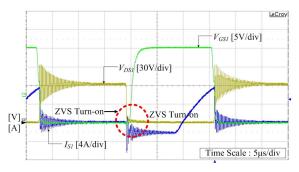

그림 5 진상 레그 스위치 S<sub>1</sub>의 ZVS 동작 Fig. 5 ZVS operation of leading-leg switch S<sub>1</sub>

그림 5는 스위치의 전압 및 전류 파형을 나타낸 그래프로, 진상 레그 스위치의 ZVS 동작을 나타낸다. 누설인덕턴스  $L_{lkg}$ 와 자화 인덕턴스  $L_m$ 에 저장된 에너지가 스위치의 역병렬 다이오드를 통해 흐른다. 이때, 스위치의 양 단의 전압이 '0'이 되어 ZVS 턴 온이 된다.

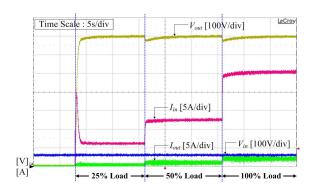

그림 6 부하 변화에 따른 컨버터 입출력 전압과 전류 Fig. 6 Input and output voltage and current according to the load variation.

그림 6은 부하 변동에 따른 컨버터의 입출력 전압과 전류를 나타낸다. 부하가 증가하더라도 전압은 일정하게 제어 되는 것 을 파형을 통해 확인하였다.

# 4. 결 론

본 논문에서는 인터리브드 풀 브릿지 컨버터와 단상 하프 브릿지 인버터를 결합한 절연형 PCS를 구현하였다. 제안된 컨 버터는 병력 입력 / 직렬 출력으로 구성하여 시스템의 효율을 개선하고 낮은 정격을 갖는 소자를 택할 수 있다. 또한, 전압 더블러 정류기를 사용해 기존 풀 브릿지 컨버터의 높은 환류 에너지, 다이오드 전압 진동, 전류 스트레스 문제를 보완하였 다. 그리고 구현된 PCS를 통해 전체 시스템이 안정되고, 효율 이 향상됨을 설계한 파라미터에 맞추어 실험하고 타당성을 검 증하였다.

본 연구는 2012년도 상업통상자원부의 재원으로 한국에 너지기술평가원(KETEP)의 지원을 받아 수행한 연구과제 (No. 20124010203300)입니다.

#### 참 고 문 헌

[1] Woo Jin Lee, "A New Phase Shifted Full Bridge Converter With Voltage Doubler Type Rectifier for High Efficiency PDP Sustaining Power Module", IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, Vol. 55, No. 6, pp. 2450 2458, 2008, June