# 비평형 그린함수 방법을 이용한 저유전-고유전-게이트-스택 구조에서의 터널링 장벽 제어

최호원, 정주영

한국과학기술원 전기 및 전자공학과, 대전광역시 305-806, 대한민국. e-mail: chw0201@kaist.ac.kr, doublejy@kaist.ac.kr

#### **ABSTRACT**

기존 플래시 메모리의 물리적 한계를 극복하여 저전압, 저전력 비휘발성 메모리 소자를 얻기 위해서는 터널링장벽 제어가 필수적이며, 저유전체와 고유전체를 적층한 VARIOT 구조는 터널링 장벽 제어에 매우 효과적이다. 우리는 비평형 그린함수 방법을 이용하여 전자 수송을 계산함으로써, VARIOT 구조가 기존의 단일 유전층 구조에비해 비휘발성 메모리 관점에서 얼마나 향상되었는지를 분석하고, 터널링 장벽 제어에 있어 고유전체가 가져야 할 가장 유리한 조건을 찾아내었다. 또한 유효질량이 에너지 장벽(유전층)의 전계 민감도와 거의 무관함을 보임으로서시뮬레이션 결과가 합리적임을 증명하였다.

### INTRODUCTION

반도체 시장에서 모바일(mobile) 기기가 강세를 보임에 따라 저전력과 안정성 관점에서 메모리의 휘발성 여부가 매우 중요한 이슈로 떠올랐다. 비휘발성 메모리의 대표 주자인 플래시 메모리(flash memory)는 저전력과 우수한 내구성을 바탕으로 반도체 시장을 성공적으로 장악하였다. 그러나 고집적화를 위한 지속적인 스케일 감소로 인해 플래시 메모리의 단일 유전층 두께는 물리적 한계에 도달 하였으며, 기존 구조로는 더 이상 미래 시장에서 요구하는 고밀도, 저전력 트랜드를 만족시키기 어려운 실정이다[1][2]. 현재 사용되는 단일 유전층 구조는 메모리 내 안정적인 전하 보존을 위해 두께를 유지해야 하므로 채널 길이 축소를 제한하며, 결과적으로 기존의 플래시 메모리가 시장이 요구하는 고밀도 트랜드를 따라가기 어렵도록 한다. 또한 두꺼운 SiO, 단일 유전층 구조는 매우 높은 지우기 /프로그래밍 동작 전압을 요구하므로 동작 전압 스케일링을 방해한다. 이러한 구조적 문제를 해결하기 위해서는 터널링 장벽 제어(Tunnel Barrier Engineering, TBE)에 의한 소자 모델링이 필수적이며, 대표적으로 Likharev가 제안한 "crested" 구조와, 저유전-고유전 물질을 적층한 Govoreanu의 VARIOT (variable oxide thickness) 구조가

있다[3][4]. 본 연구에서는 VARIOT 구조에서 Fowler-Nordheim 터널링을 이용한 해석적 모델이 아닌 비평형 그린함수 방법 (Non-Equilibrium Green's Function, NEGF)에 기반하여, 부유 게이트 로부터 실리콘 채널로 이동하는 전자에 의한 누설 전류 밀도를 계산하였다. 또한 단일 유전층 구조( $SiO_2$ )에 비해 저유전체와 고유전체를 이용한 VARIOT 구조가 얼마나 메모리에 적합한지 비교하기 위해  $V_{\scriptscriptstyle g}$  -  $J_{\scriptscriptstyle g}$  로부터 민감도(sensitivity, dec/V)를 계산 하였으며, 결론적으로 VARIOT 구조에서 터널링 장벽 제어에 가장 유리한 고유전체를 찾아내었다.

#### SIMULATION DETAILS

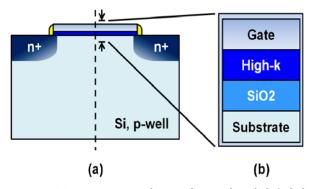

본 연구는 EDISON 나노-물리센터에서 제공하는 나노 모스펫 소자 특성 해석용 SW를 통해 수행하였다. 시뮬레이션에 사용된 구조는  $SiO_2$  만으로 이루어진 단일 유전층 구조와  $SiO_2/HfO_2$ ,  $SiO_2/ZrO_2$ ,  $SiO_2/Al_2O_3$ ,  $SiO_2/Y_2O_3$ 를 이용한 VARIOT 구조, 이렇게 두 가지로 나뉜다. 소자는 Fig. 1(a)과 같은 n-type MOSFETs 이며, 실제 계산을 수행하는 영역을 Fig. 1(b)에 간략하게 나타내었다. 모든 시뮬레이션은 3nm – EOT에 대해 수행되었다. 게이트 전극은 질화티타늄(TiN)을 가정하여 일함수로  $\Phi_{TN}$  =

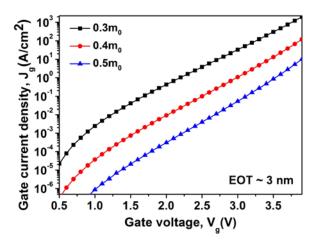

4.3eV를 사용하였으며, 실리콘에 대한 전도대 오프셋과 유전체의 유효질량은 Table. 1에 명시된 값을 사용하였다. NEGF를 이용한 전자 수송은 파라볼릭(parabolic) 밴드를 가정하고 계산되는데, 이 때 유전체와 관련된 모든 비이상적인 효과는 유효질량에 포함된다. 따라서 유전체 내 전자의 유효질량은 측정방법, 유전체의 결함 정도, 외부 환경에 따라 매우 달라지게 되며, 이러한 이유로 특정 값으로 결정된 유효질량으로부터 계산된 누설 전류의 값 자체는 부정확하거나 무의미할 수 있다(문헌마다 같은 물질에 대한 유효질량이 상당히 다름)[6]. 반면에, 유전층의 전계 민감도는 유효질량에 거의 영향을 받지 않으며, 이것은 Fig. 2에서 잘 나타나 있다. 비휘발성 메모리 관점에서 볼 때, 부유 게이트로부터의 누설 전류 레벨도 중요하지만 유전체의 전계 민감도도 매우 중요하다. 따라서, 본 논문에서는 유효질량이 전압변화에 따른 전류밀도 변화량에 거의 영향을 주지 않는다고 가정하고  $V_g - J_g$ 의 민감도  $\frac{\Delta \log(J_G)}{\Delta V_G}$  를 계산함으로써 어떤 고유전체가 VARIOT 구조를 이용한 TBE에 가장 유리한지를 정량적으로 분석하였다.

## RESULT AND DISCUSSION

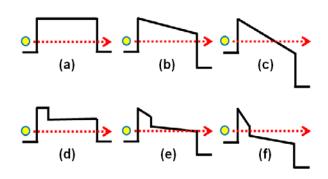

메모리의 빠른 지우기/프로그래밍과 보유 특성 향상은 MOSFETs 구조에서 게이트 하단에 위치한 유전층의 유전율에 의해 결정된다. 포아송 방정식에 따라 외부 필드가 가해질 때, 에너지 장벽(유전층)이 삼각형으로 휘게 되는데, 전계는 유전율과 반비례하므로 저유전체가 고유전체에 비해 훨씬 크게 휘게 된다. VARIOT 구조는 이러한 저유전체와 고유전체의 전계 민감도의 차이를 이용하기 위해 유전율이 다른 두 유전체를 적층하여 메모리에 응용한 구조이다. VARIOT 구조는 공급 전압이 없을 때(Fig. 2(d))와 낮을 때(Fig. 2(e)) 모두 누설 전류를 안정적인 레벨로 유지시켜 줄 뿐만 아니라, 작은 전압 상승에도 누설 전류를 급작스럽게 증가시켜 메모리 동작 속도를 향상시킨다(Fig. 2(f)).

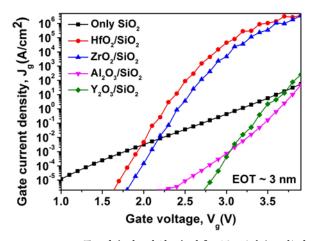

우리는 Fig. 4로부터 터널링에 의한 누설전류가 단일 SiO, 유전층 구조보다 SiO, 와 고유전체를 이용한 VARIOT 구조에서 훨씬 더 급격한 변화를 보인다는 것을 확인할 수 있다. 그래프의 검은 선이 SiO, 만 이용한 구조이며, 이것은 VARIOT 구조에 비해 그래프가 훨씬 누워있음을 알 수 있다. 또한, 같은 VARIOT 구조에서도 사용된 고유전체의 전도대 오프셋과 유전율에 따라 누설 전류가 급격히 증가하기 시작하는 지점과 그 기울기가 다르다. 예를 들어 HfO<sub>2</sub> 과 의 Y<sub>2</sub>O<sub>3</sub> 비의 누설 전류 레벨이 10<sup>-6</sup>A/cm<sup>2</sup> 에 도달하는 전압을 비교해 보자. HfO, 의 그래프(붉은 선)은 대략  $V_{g} \approx 1.6 \mathrm{V}$  에서 누설 전류 레벨이  $10^{-6}A/cm^{2}$  에 도달하는 반면,  $Y_2O_3$ 의 경우(녹색 선)  $V_g \approx 2.4$ V 에서 기준 레벨에 도달한다. 이것은 실리콘(substrate)에 대한 전도대 오프셋의 차이에서 기인한다. 같은 온도에서라면 Fermi-Dirac distribution에 의한 전자 분포가 그 위치에서의 포텐셜에만 의존하므로, 전도대 오프셋이  $1.4 \mathrm{eV}$ 인  $\mathrm{HfO}_2$  의 전류밀도가 전도대 오프셋이  $2.3eV인 Y_2O_3$ 의 경우보다 더 낮은  $V_{g}$ 에서 급격히 증가하는 것을 알 수 있다. 두 물질의 전도대 오프셋의 차이(0.9eV)가 같은 전류 레벨에서 두 물질의 전압 차이(0.8eV)와 거의 일치하는 것과 전도대 오프셋은 실험 측정 방법에 따라 조금씩 다르다는 것을 감안한다면, 실리콘에 대한 전도대 오프셋의 차이가 누설전류의 문턱 전압을 결정한다고 결론지을 수 있다. 결과적으로 같은 기울기를 갖는 물질이라면, 전도대 오프셋이 작을수록 지우기 /프로그래밍 동작전압을 낮출 수 있다.

한편, 우리는 기울기의 정량적인 비교를 위해 앞서 정의한 민감도,  $\frac{\Delta \log(J_G)}{\Delta V_G}$ 를 계산하였다. 민감도는 로그-선형 구간에서의 기울기를 구하였으며, 그 결과는 Table. 2에 나타내었다. Fig. 3에서 추측했던 것과 같이, 유전율이 큰 물질을 VARIOT 구조에

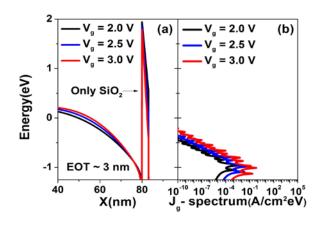

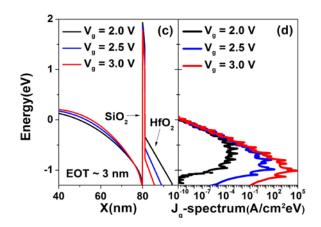

사용할수록 민감도가 향상되는 확인하였다 (Table. 1.) Fig. 5는 에너지 밴드 다이어그램과 전류밀도 스펙트럼을 민감도가 높아지는 이유를 시각적으로 잘 나타내고 있다. 참고로 전류밀도 스펙트럼, Fig. 5(b)와 Fig. 5(d)에서 나타난 그래프의 누설전류의 크기를 나타낸다. 시뮬레이션 결과, SiO, 만 사용한 구조에서는  $V_a$  에 따른 전류밀도 스펙트럼의 면적 변화가 그리 크지 않은 반면(Fig. 5(b)), HfO, 을 이용한 VARIOT 구조에선 동일한 공급 전압 변화에 따른 그 면적변화가 훨씬 큰 것을 알 수 있다(Fig. 5(d)). 이 현상을 Fig. 5(c)의 에너지 밴드 다이어그램으로 설명하면 다음과 같다. 앞의 Fig. 3에서 설명한 Fig. 5(a)와 Fig. 5(c)를 비교해보면, 단일 저유전체 구조를 사용했을 때보다 VARIOT 구조에서 게이트 전압의 변화에 따른 에너지 장벽의 두께 변화가 훨씬 크다. 에너지 장벽의 두께는 터널링을 결정하기 때문에, 이는 VARIOT 구조가 동일한 전압 변화에서 전류밀도의 변화를 유발한다는 것과 정확하게 일치한다. 즉, VARIOT 구조에서 고유전율에 대한 에너지 장벽의 전계 민감도가  $V_{o} - J_{o}$ 에서의 민감도를 결정한다.

## CONCLUSION

물리적 한계를 갖는 단일 SiO, 유전층 구조에 비해, 고유전체를 이용한 VARIOT 구조가 성능 면에 얼마나 향상될 수 있는지를 NEGF 방법을 이용한 전자 수송을 계산하여 시뮬레이션 하였다. 정량적인 지표로 민감도를 정의하여 계산한 결과, 전도대 오프셋이 낮고 유전율이 큰 물질이 메모리 성능 향상에 가장 유리하다는 것을 확인하였다. 마지막으로 게이트 전압 변화에 대한 에너지 다이어그램과 전류밀도 스펙트럼 변화를 관찰하여, VARIOT 구조가 향상된 민감도를 갖는 이유를 분석하였다.

#### REFERENCES

- [1] A. Fazio, MRS Bulletin-Materials Research Society, **29**, 814-817 (2004).

- [2] K. S. Lia, 1998 Int' l Non-Volatile Memory Technology Conference, 6 (1998)

- [3] K. K. Likharev, Appl. Phys. Lett. 73, 2137 (1998)

- [4] B. Govoreanu, Elec. Dev. Lett., IEEE 24(2), 99 (2003).

- [5] J. Robertson, Eur. Phys. J. Appl. Phys. 28, 265 (2004).

- [6] M. Specht, Solid-State Device Research Conference, 599 (2002).

Fig. 1. (a) nMOSFETs 의 구조와 (b) 시뮬레이션에서 실제 계산되는 영역의 단면.

Fig. 2.  ${

m SiO_2}$ 를 이용한 단일 유전층 구조에서 유효질량 변화에 대한  $V_s$  —  $J_s$  특성.

Fig. 3. VARIOT 구조에서 TBE 의 원리. 단일 저유전층 구조에서 공급전압이 (a) 없을 때, (b) 낮을 때, (c) 높을 때의 밴드 다이어그램. 저유전, 고유전체를 이용한 VARIOT 구조에서 공급전압이 (a) 없을 때, (b) 낮을 때, (c) 높을 때의 밴드 다이어그램.

Fig. 4.  $SiO_2$  를 이용한 단일 유전층 구조(검은 선)와  $SiO_2$  -고유전-게이트-스택(3-nm EOT) 구조에서의 물질 별  $V_g$  =  $J_g$  특성.

Fig. 5. 단일 유전층 구조(SiO<sub>2</sub>)의 (a) 에너지 밴드와 (b) 전류밀도 스팩트럼 및 VARIOT 구조(SiO<sub>2</sub>/HfO<sub>2</sub>)의 (c) 에너지 밴드와 (d) 전류밀도 스펙트럼. (b)와 (d)의 X 축은 로그 스케일을 사용하였음.

Table. 2. 시뮬레이션에 사용된 유전체들의 유효질량  $(m^*)$ 과 실리콘에 대한 전도대 오프셋(CB offset)[5].

|                   | SiO <sub>2</sub> | HfO <sub>2</sub> | ZrO <sub>2</sub> | $Al_2O_3$ | $Y_2O_3$ |

|-------------------|------------------|------------------|------------------|-----------|----------|

| $m^* (m_0)$       | 0.43             | 0.2              | 0.2              | 0.2       | 0.25     |

| CB offset<br>(eV) | 3.2              | 1.4              | 1.5              | 2.8       | 2.3      |

Table. 2. 유전체의 유전율(K)과 그에 대한 Fig. 4의 민감도(sensitivity).

|                                                  | SiO <sub>2</sub> | $HfO_2$ | ZrO <sub>2</sub> | $Al_2O_3$ | $Y_2O_3$ |

|--------------------------------------------------|------------------|---------|------------------|-----------|----------|

| $\mathrm{K}(\varepsilon_{\scriptscriptstyle 0})$ | 3.9              | 25.0    | 25.0             | 9.0       | 15.0     |

| Sensitivit                                       |                  |         |                  |           |          |

| У                                                | 2.33             | 9.80    | 8.98             | 5.95      | 8.04     |

| (dec/V)                                          |                  |         |                  |           |          |