# 시간-도메인 비교기를 이용하는 10-bit 10-MS/s 0.18-um CMOS 비동기 축차근사형 아날로그-디지털 변환기

정연호\*· 장영찬\*

\*금오공과대학교

A 10-bit 10-MS/s 0.18-um CMOS Asynchronous SAR ADC with Time-domain Comparator

Yeon-ho Jeong\* · Young-Chan Jang\*

\*Kumoh National Institute of Technology

E-mail : ycjang@kumoh.ac.kr

요 약

본 논문은 rail-to-rail 입력 범위를 가지는 10-bit 10-MS/s 비동기 축차근사형 (SAR: successive approximation register) 아날로그-디지털 변환기 (ADC: analog-to-digital converter)를 제안한다. 제안된 SAR ADC는 커패시터 디지털-아날로그 변환기 (DAC: digital-to-analog converter), SAR 로직, 그리고 비교기로 구성된다. 외부에서 공급되는 클럭의 주파수를 낮추기 위해 SAR 로직과 비교기에 의해 비동기로 생성된 내부 클럭을 사용한다. 또한 높은 해상도를 구현하기 위해 오프셋 보정기법이 적용된 시간-도메인 비교기를 사용한다. 면적과 전력소모를 줄이기 위해 분할 캐패시터 기반 차동 DAC를 사용한다. 설계된 비동기 SAR ADC는 0.18-um CMOS 공정에서 제작되며, core 면적은 420x140 μm²이다. 1.8 V의 공급전압에서 0.818 mW의 전력소모와 91.8 fJ/conversion-step의 FoM을 가진다.

#### **ABSTRACT**

This paper describes a 10-bit 10-MS/s asynchronous successive approximation register (SAR) analog-to-digital converter (ADC) with a rail-to-rail input range. The proposed SAR ADC consists of a capacitor digital-analog converter (DAC), a SAR logic and a comparator. To reduce the frequency of an external clock, the internal clock which is asynchronously generated by the SAR logic and the comparator is used. The time-domain comparator with a offset calibration technique is used to achieve a high resolution. To reduce the power consumption and area, a split capacitor-based differential DAC is used. The designed asynchronous SAR ADC is fabricated by using a 0.18 um CMOS process, and the active area is  $420x140~\mu m^2$ . It consumes the power of 0.818 mW with a 1.8 V supply and the FoM is 91.8 fJ/conversion-step.

# 키워드

SAR ADC, Asynchronous SAR, successive approximation, time-domain comparator

## 1. 서 론

최근 많은 분야에서 저전력에 대한 관심이 높 아지면서 이에 적합한 축차근사형 (SAR: successive approximation register) 아날로그-디지털 변환기 (ADC: analog-to-digital converter)가 큰 주목을 받고 있다. 기존의 SAR ADC는 낮은 sampling rate 때문에 센서 인터페이스나 바이오 응용분야에 국한되었으나 최근에는 수십 ~ 수백 MHz까지 sampling rate를 가지는 SAR ADC가 연구되면서 pipeline ADC의 영역이었던 비디오, 통신응용분야에 적용하게 되었다.

본 논문에서는 SAR ADC를 구현함에 있어 Nyquist rate의 sampling clock frequency를 이용하기 위해 비동기방식을 선택하였다. 기존의 SAR ADC에서는 10-bit을 구현하기 위해 reset, sample 구간을 포함하여 12 cycle이 요구되고, 이에 따라 sampling rate의 10 배 이상의 클럭 주파수가 필요하다. 이러한 이유로 SAR ADC의 sampling rate는 제한될 수밖에 없었다. 하지만 비동기 방식을 사용하게 되면 이 문제를 해결할 수 있다. 이는 외부 클럭에 의해 내부적으로 클럭을 생성하여 ADC를 동작시키는 방식으로 클럭의 한 주기마다 아날로그 입력을 샘플하기 때문에 sampling rate를 향상시킬 수 있다.

제안하는 10-bit 10-MS/s 비동기 SAR ADC는 rail-to-rail input range를 가지고 split based-capacitor differential DAC, time-domain comparator, SAR logic으로 구성되며, 1.8V supply의 0.18-um CMOS 공정에서 설계된다.

# Ⅱ. 비동기 SAR ADC 구조

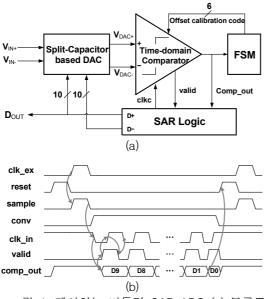

제안하는 10-bit 10-MS/s 비동기 SAR ADC는 그림 1(a)과 같은 블록도와 같이 time-domain comparator, split capacitor-based differential DAC, SAR logic, 그리고 FSM으로 구성된다. 축 차근사의 동작을 위한 내부 클럭은 외부 클럭으로부터 비동기 SAR logic과 comparator의 동작에 의해 생성된다. 그림 1(b)는 비동기 SAR ADC의타이밍도이다. ADC는 10 번의 데이터 변환이 끝난 후에는 reset 모드를 유지하여 전력소모를 최소화하고, 다음의 외부 클럭에 의해 새로운 입력을 샘플한다 [1].

그림 1. 제안하는 비동기 SAR ADC (a) 블록도 (b) 타이밍도

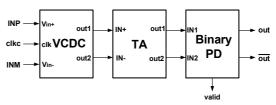

그림 2. Time-domain comparator의 블록도

그림 2는 time-domain comparator의 블록도로 voltage controlled delay converter (VCDC), time amplifier (TA), 그리고 binary phase detector (binary PD)로 구성된다. DAC에서 출력된 voltage difference를 VCDC를 이용하여 time difference로 변환시키고, TA에서 time difference를 증폭한다. 그리고 binary PD에서 time difference를 비교하여 디지털 값으로 변환한다.

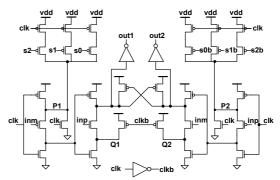

그림 3. Differential voltage controlled delay converter

그림 3은 제안하는 VCDC의 회로도이다. clk이 high일 때, VCDC는 pre-charge 구간으로 out1, out2는 0을 출력하게 된다. clk이 low일 때, out1 과 out2는 1을 출력하게 되는데 입력의 voltage difference에 의해 출력이 high로 천이되는 시점 이 다르게 되어 time difference를 만들 수 있다. 비교가 끝난 후 clk이 다시 high가 되어 pre-charge 구간이 되면 P1, P2, Q1, Q2 노드는 floating 상태가 된다. 다음의 정확한 비교를 위해 P1, P2 노드는 0 V가 되고 Q1, Q2 노드는 V<sub>DD</sub>가 될 수 있도록 switch를 삽입하였다. 설계된 SAR ADC는 한 개의 comparator를 사용하고, 그 특성 이 전체 ADC의 성능에 매우 중요하기 때문에 comparator의 offset을 제거하기 위해 VCDC에 offset 보정 회로를 추가하였다. 표 1은 보정 code 에 따른 comparator의 offset 변화를 보여준다. Default code는 011이고, 이 경우 offset은 0이다. 공정이나 외부의 요인에 의해 offset이 생기게 되 면 FSM을 통해 offset이 0이 될 수 있는 code를 찾아 저장하게 되어 comparator의 offset을 줄이 도록 한다. 이 코드는 한 스텝당 대략 3.5 mV의 offset을 조절할 수 있다.

## 丑 1. Comparator offset calibration table

그림 4. Split-capacitor based differential DAC

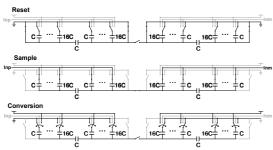

그림 4는 split-capacitor based DAC의 회로도 이다. 중간에 위치한 unit capacitor C에 의해 반으로 접힌 형태로 전체 capacitance는 binary type에 비해 크게 감소된다. Reset 모드에서 DAC의 출력은 0으로 초기화된다. Sample 모드에서 bootstrapped NMOS switch에 의해 통과한 입력은 capacitor의 bottom에 연결되고, rail-to-rail 입력 전압에서 DAC의 출력은 서로 연결되어  $V_{DD}/2$ 로 나오게 된다. Conversion 모드에서는 내부 클럭에 의해 10 번의 cycle 동안 switching되어 DAC 출력은 입력을 찾아가며  $V_{DD}/2$ 로 수렴하는 동작을 수행한다 [2].

#### Ⅲ. 시뮬레이션 결과

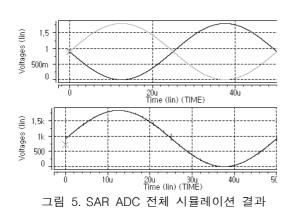

그림 5는 SAR ADC 전체 시뮬레이션으로 첫 번째 그림은 sine wave의 입력이고, 두 번째 그 림은 ADC에서 출력한 디지털코드로 그린 파형이

다. SAR ADC의 출력 파형에 포함된 glitch는 SAR logic에서 발생되는 노이즈인데, 실제 ADC 의 성능에는 영향을 주지 않는다.

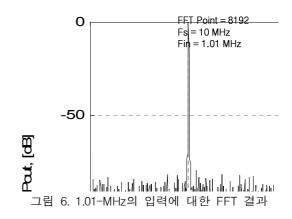

그림 6은 1.01-MHz의 입력에 대해 8192 point 로 FFT를 수행한 결과이다. 1.8 V 10-MS/s의 sampling 속도에서 60.85 dB의 SNDR과 9.8-bit의 ENOB를 나타내었다.

## IV. 결 론

제안한 10-bit 10-MS/s asynchronous SAR ADC는 1.8 V supply와 rail-to-rail 입력 범위를 가지고 0.18-um CMOS공정에서 설계되었다. 비동기 방식을 사용하여 속도를 개선하였다. 그리고 비동기임에도 불구하고 time-domain comparator를 사용하였고 offset 보정기법을 추가하여 comparator의 성능을 향상시켰다. 설계된 SAR ADC의 성능은 1.8-V<sub>P-P</sub> 1.01-MHz의 입력신호에 SNDR은 60.85 dB이고 ENOB는 9.8-bit을 나타내었으며, 전력소모는 0.818 mW이다.

### 감사의 글

This research was supported by the Basic Science Research program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (2010-0006314), the IT R&D program of MKE/KEIT (10039159), and IDEC.

### 참고문헌

[1] C.C. Liu, et. al., "A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731-740, Apr. 2010.

[2] S.k. LEE, et. al., "A 1.3uW 0.6V 8.7-ENOB Successive Approximation ADC in a 0.18um CMOS," *IEEE ISSCC*, pp. 242-243, 2009