## 비대칭 스페이싱 다중채널 구조를 이용한 다결정 실리콘 박막 트랜지스터

**송승민**, 최성환, 한민구 서울대

# Multiple-Channel using Asymmetric Spacing Structure (ASS) Polycrystalline Silicon (Poly-Si) Thin-Film Transistors (TFTs)

Seung Min Song, Sung-Hwan Choi, Min-Koo Han Seoul National University

Abstract - 높은 케이트와 드레인 바이어스 스트레스 조건에서 신뢰성을 높이기 위해 비대청 스페이성 다중채널 구조 (ASS)를 이용한 다결정 실리콘 박막 트래지스터 (poly-Si TFTs)를 제안하였다. 이것은 어떠한 추가공정 없이 제작할 수 있고 채널 가운데 부분의 넓은 공간을이용하여 소자안의 유도된 열을 방출할 수 있기 때문에 기존의 트랜지스터에 비해 47%의 문턱전압감소와 3%의 이동도 변화 감소를 보인다.이 실험결과는 제안된 소자구조가 기존의 소자에 비해 높은 케이트와드레인 바이어스 조건에서 전기적 특성이 더 안정적 이라는 것을 보여준다.

#### 1. 서 론

최근 차세대 디스플레이인 AMOLED의 구동조건에 맞는 박막 트렌지스터로 저온도 다결정 실리콘 박막 트랜지스터 (LTPS TFTs) 가 상당한 주목을 받고 있다. 그 이유는 캐리어의 이동도가 큰 다결정 실리콘 박막 트랜지스터 (poly-Si TFTs) 가 AMOLED에 적합한 높은 전류구동이 가능하기 때문이다 [1]. 그러나 다결정 실리콘 박막 트랜지스터는 트랜지스터안의 그레인과 그레인 바운드리로 인한 트랩 스테이트 때문에 높은 전기적 스트레스 후 소자의 안정성이 낮아지는 특성을 보인다. 또한 소자 내 전류의 호름을 통해 유도된 열이 채널 안에서 실리콘과수소의 결합을 깨뜨려 트랩 스테이트를 추가시킨다 [2]. 이러한 문제를 개선시키기 위해서 본 논문에서는 비대칭 스페이싱 다중채널 구조(ASS)를 이용한 다결정 실리콘 박막 트랜지스터 (poly-Si TFTs)를 제안하고 제작하였다. 지금까지 소자의 신뢰성을 향상시키는 몇몇 연구들이 있었지만 이것들은 추가적인 공정이 필요하였다 [3]-[4]. 하지만 본 논문은 어떠한 추가적인 공정이 필요치 않고 소자의 안정성을 향상 시킬 수 있다는 장점이 있다.

#### 2. 본 론

### 2.1 순차적인 측면 결정화 (SLS) 과정을 통한 다결정 실리콘 박막트 랜지스터 제작

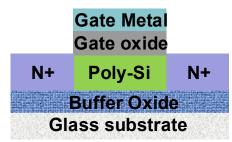

우리는 그림 1과 같이 SLS 과정을 통한 기존의 저온도 (450℃) 탑 게이트 다결정 실리콘 박막 트랜지스터를 제작하였다. 우선 유리기판 위에실리콘 옥사이드 (SiO₂) 완충층을 쌓고 플라즈마를 이용한 화학 기상증작법 (PECVD)을 통해서 50nm 두께의 아모르포스 실리콘(a-Si) 활성층을 증착시켰다. 308 nm XeCl 엑시멀 레이져를 이용한 SLS 결정화과정동안 잔여 수소를 제거하기 위한 탈수소반응 (Dehydrogenation)을 수행하였고 레이져 조사 후 채널층 안의 다결정 실리콘 막을 패터닝해주었다. 게이트 산화물은 100 nm 두께로 PECVD방식을 이용해 증착시켰다.

<그림 1> SLS 방식을 이용한 다결정 실리콘 박막 트랜지스터 구조

2.2 실험 결과 및 논의

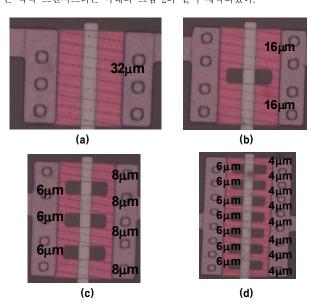

SLS 방식과 다중채널 구조을 이용한 n 타입과 p 타입의 다결정 실리콘 박막 트랜지스터는 아래의 그림 2와 같이 제작되었다.

<그림 2> SLS 방식을 이용한 기존의 (a) 단채널 (b) 2중채널 (c) 4중채널 (d) 8중채널 다결정 실리콘 박막트랜지스터

위 그림과 같이 이 실험에서는 채널의 폭과 길이의 비율 (W/L) 을 똑같이 하였다. (단채널 구조 (32/4) μm, 2중채널 [(16×2)/4] μm, 4중채널 [(8×4)/4] μm, 8중채널 [(4×8)/4]μm) 위 트랜지스터들의 이동도는 약 52 cm²/ (V•s) 정도 나온다.

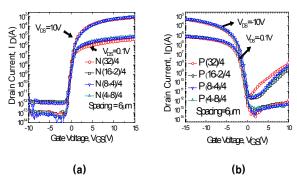

p 타입과 n 타입으로 모두 제작된 위의 트랜지스터들의 특성 곡선은 그림 3과 같다. 암실조건에서 모든 전기적 특성을 관찰하 기 위해서 HP4156B 반도체 분석기를 이용하였다.

<그림 3> 기존의 단채널과 다중채널 다결정 실리콘 박막 트랜지스터의 (a) n 타입 과 (b) p 타입의 특성 곡선

위의 그림 3에서 보는 바와 같이 스트레스를 가하지 않은 상태에서 기존의 단채널과 다중채널 트랜지스터의 전기적 특성은 비슷하다. 트랜지스터의 크기가 줄어들수록 채널 안 드레인 쪽의 영향은 커진다. 소자가 높은 포화상태 (높은 게이트와 드레인 바이어스 상태) 에서 동작할 때 소자안의 온도가 증가한다는 것은 이미 알려져 있다 [5]. 다결정실리콘 박막 트래지스터에서 높은 드레인 전압 때문에 충격이온화(Impact Ionization) 가 생기고 그것은 전자전공쌍을 생성시켜 채널안의전류의 흐름을 방해 한다 [5]-[6].

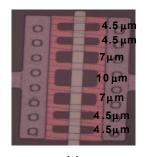

이러한 소자안의 열적문제를 해결하고 신뢰성을 향상시키기 위하여 위 논문에서는 비대청 스페이성 (ASS) 다중채널 구조를 이용한 다결정실리콘 박막 트랜지스터를 고안했다. 이것은 채널의 폭과 길이의 비율은 (32/4)  $\mu$ m 로 고정시키되 부채널 사이의 공간의 크기를 다르게 하여 제작한 것이다. 그림 4에서 나와 있는 것과 같이 그림 4(a) 는 부채널 사이의 가운데 공간영역을 크게 한 것이고 그림 4(b)는 양쪽 끝부분의 공간영역을 크게 한 것이다. 이 고안된 트랜지스터들은 채널층의 형성시마스크의 패턴만 바꾸어 주면 되기 때문에 어떠한 추가적인 공정도 필요하지 않다.

(a) (b) <그림 4> (a) ASS 타입−1, (b) ASS 타입−2 다중채널 다결정 박막 실리콘 트랜지스터

제안된 소자는 채널들 사이의 여러 간격으로 인해서 드레인 접합 근처 캐리어들의 움직임과 충격이온화를 줄일 수 있고 여러 동작 조건하에서 소자의 신뢰성을 향상 시킬 수 있다.

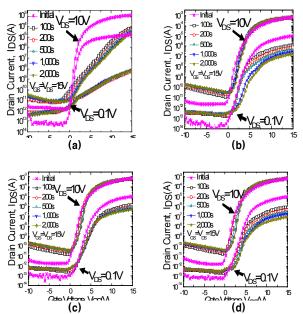

<그림 5> 높은 게이트와 드레인 바이어스 스트레스(V<sub>GS</sub> = V<sub>DS</sub> = 15 V for 2,000s) 전후 TFT의 특성 곡선 (a) 단채널 , (b) 8중채널, (c)ASS 타입-1, (d)ASS 타입-2

유도된 열이 전체채널을 따라 흐르는 전류의 양과 많은 관계가 있기때문에 그것을 잘 분배시켜주기 위해서 우리는 다중채널 개념을 도입하였다. 이 경우에 각 부채널 사이의 공간으로 열을 방출 시킬 수 있고 그공간의 크기에 따라 방출되는 열의 양도 달라질 수 있다. 소자의 동작특성을 확인하는 과정에서 채널의 가운데 부분에 열이 집중된다는 것을 알 수 있었고 가운데 집중된 열의 분산효과와 부채널 사이의 공간과의관계를 알아보기 위하여 그림 5에 나와 있는 것과 같이 기존의 단채널(공간없음), 8중채널(6 /㎜), ASS 타입-1(10/㎜), ASS 타입-2(4/㎜)들의 특성을 각각 비교하였다. 그림 2(a)(d)와 그림 4(a)(b)에서 볼 수 있는 것과 같이 트랜지스터들의 채널 가운데 부분의 공간의 크기가 다르

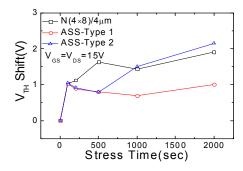

다는 것을 알 수 있다. 그림 5는 각 트랜지스터들에 스트레스를 걸은 전후의 특성곡선을 나타낸다. 스트레스는 게이트와 드레인에 2000초 동안 각각 15V씩 인가하였다. 그림 5에서 보는 바와 같이 스트레스를 걸은후 기존 8중채널 다결정 실리콘 TFT의 문턱전압은  $V_{DS}$  가 0.1V 일 때 1.91V 증가하였고 ASS 타입-1 과 ASS 타입-2 는 각각 1.00V, 2.15V씩 증가하였다.

<그림 6> 스트레스 인가 후 기존 8중채널의 TFT와 제안된 TFT의 문턱전압의 변화비교 (V<sub>GS</sub> = V<sub>DS</sub> = 15 V for 2,000s)

제안된 ASS 타입-1 TFT는 위의 조건하에서 기존의 8중채널 TFT보다 문턱전압의 이동이 약 47% 감소하였다. 이것은 제안된소자가 전류를 유지하는데 더 작은 전압이 필요함을 나타내고다결정 실리콘 TFT의 동작온도와 전력소비가 감소함을 의미한다. 제안된소자는 채널 가운데 부분의 넓은 공간을 이용함으로서 소자안의 열을 방출할 수 있고 그에 따라 높은 전류 스트레스 조건으로 부터 다결정 실리콘 TFT의 온도 상승을 완화 시킬수 있다.

#### 3. 결 론

우리는 추가적인 공정 없이 여러 개의 부채널 사이에 다른 크기의 공간을 갖는 비대칭 스페이싱 구조를 이용한 TFT를 제안하고 제작했다. 제안된 소자는 열이 집중 되는 전체 채널의 가운데 부분에 공간을 채택하고 그것을 넓힘에 따라 소자 가운데 부분의 열을 효과적으로 분배할수 있었다. 이것으로 인해 소자의 드레인 접합 근처의 온도상승을 효율적으로 감소시킬 수 있었다. 실험에서 제안된 소자가 높은 게이트와 드레인 바이어스 스트레스 이후 기존의 TFT보다 문턱전압이 47% 감소함에 따라 신뢰성을 향상시킬 수 있다는 것도 확인하였다. 그러므로 제안된 소자는 높은 성능의 AMOLED의 응용에 더욱 적합하다.

#### [참 고 문 헌]

- [1] A. Kumar K. P. and J. K. O. Shin, "A simple TFT technology for display systems on glass", in IEDM Tech. Dig., pp. 515, 1997.

- [2] S. Inoue, H. Ohshima, and T. Shimoda, "Analysis of threshold voltage shift caused by bias stress in low temperature poly-Si TFTs," in IEDM Tech. Dig., pp. 527530,1997.

- [3] X. Zeng, X. W. Sun, J. Li, and J.K.O. Sin, "Improving reliability of poly–Si TFTs with channel layer and gate oxide passivated by NH<sub>3</sub>/N<sub>2</sub>O", Microelectronics Reliability, Vol. 44, Issue 3, pp. 435–442, 2004.

- [4] M.-W. Ma, C.-Y. Chen, C.-J. Su, W.-C. Wu, T.-Y. Yang, K.-H. Kao, T.-S. Chao, and T.-F. Lei, "Improvement on performance and reliability of TaN/HfO<sub>2</sub> LTPS-TFTs with fluorine implantation", Solid-State Electronics, Vol. 52, pp.342–347, 2008.

- [5] S. Inoue, M. Kimura and T. Shimoda., "Analysis and Classification of Degradation Phenomena in Polycrystalline-Silicon Thin Film Transistors Fabricated by a Low-Temperature Process Using Emission Light Microscopy", Jpn. J. Appl. Phys., vol. 42, pp. 1168–1172, 2003.

- [6] S.-H Choi, S.-J. Kim, Y.-G. Mo, H.-D. Kim, and M.-K. Han, "Reliability in Short-Channel p-Type Polycrystalline Silicon Thin-Film transistors under High Gate and Drain Bias Stress", Jpn. J. Appl. Phys., vol. 49, no. 3, pp.03CAos-1~03CA04-6, 2010