# 인접선 신호선의 누화(Crosstalk)에 대한 해석 및 회로 모델에 관한 연구

**이동재** , 하정래 , 김종민 , 나완수 성균관대학교 정보통신공학부

# Study of Crosstalk in Multi-conductor system and Equivalent Circuit Model

Dongjae Lee , Jungrae Ha . Jongmin Kim . Wansoo Nah School of Information and Communication Engineering Sungkyunkwan University

Abstract- 본 논문에서는GaAs-Transistor가 접합된 전송선로 사이에서 발생되는Crosstalk의 영향에 관한 연구를 하였다.이 모델의 해석을 위해 인접선에서의Crosstalk의 이론적인 접근을 하고,3D FullWave시뮬레이션과Circuit시뮬레이션을 통해 해석하는Crosstalk의 해석방법에 대한 모델을 제시하고자 한다.또한 Coupling 된 SolderBump의EquivalentCircuitModel을 제시함으로써 SolderBump의 Coupling의Crosstalk의 영향에 미치는 영향에 대해 규명하고자 한다.

#### 1. 서 론

송신단에서 전송선로로 신호를 보냈을 때 그 주위에 전계와 자계가 발생하게 되고 그로 인해 인접한 전송선로에 Noise가 유기된다. 유기된 Noise는 선로간 거리가 가까울수록, 회로의 동작 속도가 빠를수록 더 크게 발생된다. 이렇게 발생된 신호의 간섭을 인접선누화(Crosstalk)라고하며 현재 전자제품의 소형화와 고속화 트렌드에 맞물려 회로설계에서 매우 큰 문제로 부각되고 있다. 인접한 전송선로가 Noise의 Source가되면 아무리 외부의 전자파방해를 차단한다 하더라도 인접한 선로의 신호전송을 방해하게 되고 결국 회로의 오동작으로 이어지므로 Crosstalk 문제는 매우 심각하다 하겠다.

이에 본 연구에서는 인접선이 GaAs-Transistor와 Solder Bump로 연결된 Multi-Conductor System에서 Solder Bump의 Coupling의 영향이 인접선의 Crosstalk에 어떠한 영향을 미치는가에 대한 연구를 진행하였다.

# 2. 본 론

## 2.1 인접선에서 Coupling에 의한 Crosstalk

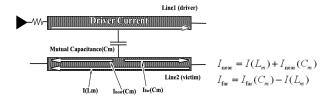

Crosstalk는 Coupling에 의해 인접한 선로에 원하지 않는 Noise를 발생시킨다. Noise의 발생 원인으로는 선로주위에 발생되는 자기장에 의한 Mutual Inductance와 전기장에 의한 Mutual Capacitance가 있다. 또한 Noise가 발생되는 장소에 따라 Near-end 와 Far-end Crosstalk로 구분할 수 있다. 그림 2.1에서 Noise의 발생 원인과 측정 위치에 따라 발생된 Noise를 나타내었고, Mutual Inductance와 Mutual Capacitance에 의한 Near-end 와 Far-end 에서의 Noise의 크기는 식 2.1과 같이 유도할수 있다. [1]

$$V_{\scriptscriptstyle X} = V_{\scriptscriptstyle crosstalk} \Biggl( 1 + \frac{R - Z_{\scriptscriptstyle 0}}{R + Z_{\scriptscriptstyle 0}} \Biggr), \quad Z_{\scriptscriptstyle 0} = \sqrt{\frac{L}{C}}, \quad V_{\scriptscriptstyle input} = \frac{V_{\scriptscriptstyle s}}{2}, \quad T_{\scriptscriptstyle D} = X \sqrt{LC}$$

${\cal L}$  and  ${\cal C}$  are self-inductance and capacitance per unit length.

$$\begin{split} I_{near} &= I\left(L_{\mathit{m}}\right) + I_{near}\left(C_{\mathit{m}}\right) \\ V_{near} &= \left(L_{\mathit{m}}X\right) \frac{dI_{\mathit{driver}}}{dt} + \left(C_{\mathit{m}}X\right) \frac{dV_{\mathit{driver}}}{dt} \cdot \frac{Z_{0}}{2} \\ &= \frac{V_{input}}{4} \left(\frac{L_{\mathit{m}}}{L} + \frac{C_{\mathit{m}}}{C}\right) \end{split}$$

$$\begin{split} I_{far} &= I_{far}\left(C_{m}\right) - I\left(L_{m}\right) \\ V_{far} &= \left(C_{m}X\right) \frac{dV_{driver}}{dt} \cdot \frac{Z_{0}}{2} - \left(L_{m}X\right) \frac{dI_{driver}}{dt} \\ &= -\frac{V_{input}X\sqrt{LC}}{2T_{r}} \left(\frac{L_{m}}{L} - \frac{C_{m}}{C}\right) \end{split}$$

< 식 2.1 Near-end 와 Far-end에서의 Noise의 크기 >

이 식은 Victim line의 Near-end와 Far-end에서의 매칭상태에 의해 여러 형태로 변형된다. 즉, 매칭이 되었을 경우 반사가 일어나지 않아 식 2.1식 그대로 Crosstalk를 나타낼 수 있지만, 어느 한쪽이 매칭이 되지 않았을 경우 발생된 Noise는 반대편으로 반사 되어 발생된 Crosstalk 식 2.1과는 다르게 표현된다. 식 2.1에서 필요로 되는 인접한 전송선로에서 Crosstalk에 영향을 미치는 단위길이당의 Mutual Inductance( $L_m$ )와 Mutual Capacitance( $C_m$ )는 해석 툴인 LINPAR를 사용하여 구할 수 있다. 구해진 값들은 매트릭스 형태로 나타내어지고, 그 값들을 Victim line의 매칭상태 변화에 따른 Crosstalk식에 대입하면 수식을 통해 발생되는 Crosstalk의 크기를 계산할 수 있다.

# 2.2 Crosstalk의 시뮬레이션 측정모델

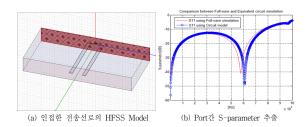

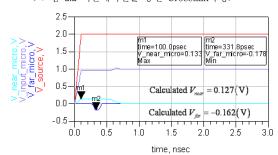

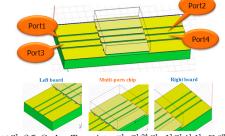

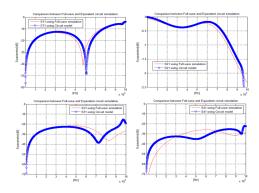

Crosstalk에 의한 Noise를 해석하기 위해 Ansoft사의 Full wave simulator인 HFSS를 이용하여 그림 2.2(a) 와 같이 모델링한고 인접선간의 전달특성을 확인하기 위해 S-parameter를 측정하였다. 그림 2.2(b)는 인접선의 S-parameter를 나타내었다. 이 모델의 Far-end와 Near-end에서의 Noise를 측정하기 위해 Circuit simulator인 ADS(Advanced Design System)로 인접선을 Circuit Modeling을 하고, 측정된 S-parameter를 삽입하였다. 그림 2.3은 측정된 Noise의 크기를 나타내었다. 발생된 Noise의 peak 값이 식 2.1을 이용한 값과 일치하는 것을 확인 할 수 있다.

< 그림 2.1 Crosstalk에 의한 Noise의 발생 >

< 그림 2.2 시뮬레이션을 통한 Crosstalk측정>

< 그림 2.3 수식과 시뮬레이션을 통한 Crosstalk값의 비교>

## 2.3 Multi-Conductor System에서 GaAs-Transistor가 접합된 인 접선에서 Solder Bump의 Coupling에 의한 Crosstalk의 영향

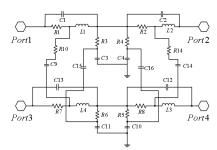

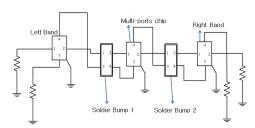

인접한 전송선과 GaAs-Transistor가 접합한 부분에서 Solder bump의 Coupling에 의한 Crosstalk의 영향을 분석하기 위해 Coupling된 Solder bump를 설계하였다. Solder bump에서 발생하는 Crosstalk의 특성을 정 량적으로 분석하기 위해서 그림 2.4와 같이 Solder bump의 Mutual 성 분들을 고려한 회로 모델을 구성하였다. 회로 모델을 구성하기 위해서 단일 선로에 대한 회로 모델을 T모형으로 구성하였고[2] 구성된 모델의 Mutual 성분인 capacitance은 S-parameter에 Optimization을 이용해서 추출을 하였다. 추출된 결과는 표 1과 같이 정리하였다. Solder bump에 대한 Mutual 성분들을 고려한 후에는 그림 2.5와 같이 각각의 Microstrip line과 Chip에 대해서 Full-wave 시뮬레이션을 통해 값을 구 하였고, 그 결과를 그림 2.6의 4포트 Flip chip에 대한 회로 모델에 삽입 함으로써 Solder bump의 영향이 고려된 Circuit Model을 설계하였다. Solder bump의 영향을 고려하기 위해서 그림 2.5에서와 같이 3부분으로 나눠서 측정된 S-parameter를 네트워크에 각 부분에 삽입하였다. 그림 2.7에서는 그림 2.4의 Solder Bump를 고려한 S-parameter와 Full-wave 시뮬레이션을 통해 얻어진 S-parameter 를 비교하였다. 두 S-parameter 가 거의 일치하는 것을 확인 할 수 있다.

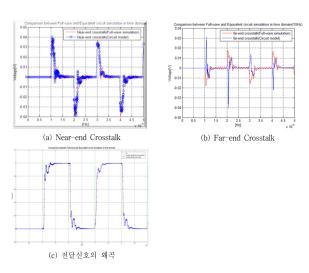

### 2.4 Time-domain 시뮬레이션

제시된 모델에 의해 측정된 S-parameter를 이용하여 Time-domain에서 시뮬레이션을 통해 얻어진 값을 비교한 그래프를 그림 2.7에 도시하였다. Time-domain에서도 Frequency-domain 과 같이 Full Wave 시뮬레이션과 Solder Bump의 Equivalent Circuit Model을 사용한 Circuit 시뮬레이션이 매우 일치하는 것을 확인 할 수 있다.

< 그림 2.4 Solder bump의 Equivalent Circuit >

| R_bump   | R1,R2,R7,R8   | 0.0374   | ohm |

|----------|---------------|----------|-----|

| L_bump   | L1,L2L3,L4    | 0.1896   | nΗ  |

| C_bump   | C1,C2,C12,C13 | 6.9093   | fF  |

| R_gnd    | R4,R3,R5,R6   | 20.2293  | ohm |

| C_gnd    | C3,C4,C10,C11 | 22.2156  | fF  |

| C_mu1    | C9            | 0.00383  | pF  |

| C_mu2    | C14           | 0.003083 | pF  |

| C_mu3    | C15           | 0.001    | pF  |

| C_mu4    | C16           | 0.001    | pF  |

| R_cross1 | R10,          | 503.823  | ohm |

| R_cross2 | R14           | 503.625  | ohm |

<표 1 Soder bump의 Equivalent Circuit 컴포넌트 값>

< 그림 2.5 GaAs-Transistor가 접합된 인접선의 모델링 >

< 그림 2.6 Interconnection된 인접선의 네트워크 모델 >

< 그림 2.7 HFSS 모델과 Equivalent모델의 port간 S-parameter 비교 >

< 그림 2.8 HFSS 와 Equivalent Circuit의 Time-domain 비교 >

#### 3. 결 론

본 논문에서는 고속 신호 전송 시 인접선에서 발생되는 Mutual 성분에 의한 Crosstalk 현상을 이론적 접근과 시뮬레이션을 통해 얻어진 값이서로 일치한다는 것을 확인하였다. 확인된 결과를 토대로 Crosstalk 측정 시뮬레이션 모델을 제시하였으며, 실제 모델에서 적용될 수 있는 Multi-ports flip-chip에 대한 Full-wave 시뮬레이션을 구성하고 해석하였다. 해석된 결과를 이용해서 Mutual 성분이 고려된 Solder bump에 대해 회로모델링을 하였고 모델링 한 결과가 주파수 영역에서의 특성인 S-parameter가 잘 일치하였고, 시간영역에 대해서도 잘 일치하고 있는 것을 확인하였으며 본 연구결과를 통해서 Multi-ports flip-chip의 Crosstalk에 대해서 정량적으로 분석할 수 있다.

### [참 고 문 헌]

[1] Stephen H. Hall, Garrett W. Hall, James A McCall, "High-Speed Digital System Design: A

Handbook of Interconnect Theory and Design Practices," John Wiley & Sons, Inc.,  $2000\,$

[2] Hoon Hwangbo, Jaehoon Lee, Wansoo Nah, Jinho Joo, Seung-Boo Jung, "Modeling of Flip-Chip Interconnects Using Novel Neural Network Approaches", 2005 Asia-Pacific Microwave Conference Proceedings (APMC2005), pp 1303–1306, December 4–7, 2005, Suzhou, China

[3] Jongmin Kim, Jin-keon Yu, Byong Su Seol, JongSung Lee, Wansoo Nah, "High Frequency Signal Transfer Characteristic of a 40-pin FPC Connector", The 8th International Symposium on Antennas, Propagation and EM Theory, IEEE, pp1255–1258, Kunming, CHINA, November 2–5, 2008