# SoC 기반 DC Motor의 속도제어 연구

\*박인수, \*김정옥, \*\*박광현, \*\*\*Khalifa Eltayeb kh Mustafa \*(주)이씨엠, \*\*충주대학교 전자통신과, \*\*\*University Technology Malaysia

### Study of Speed Control DC Motor Based SOC

\*Park In-Soo, \*Kim Jung-Ok, \*\*Park Kwang-Hyeon, \*\*\*Khalifa Eltayeb kh Mustafa \*Inc. ECM, \*\*Chungju National University, \*\*\*University Technology Malaysia

Abstract - 본 논문에서는 PID, PWM, HSC, 컴퓨터와의 호스트통신, 외부 DAC 인터페이스를 FPGA만을 이용하여 하나의 Chip에 구현하고 DC 서보 모터의 속도를 설정한 제어 상태로 안정화시킬 수 있는 시스템을 구현하고자 한다. 컴퓨터에서 설정한 설정치(SV)와 P, I, D의 이득 값을 호스트 통신으로 데이터 블록은해당 블록으로 전달하며 DC 서보 모터의 엔코더에서 나오는 90°위상차가 있는 2채널의 펄스는 HSC 블록을 거쳐 프로세스치(PV)를 생성하고 이로부터 얻어진 SV와 PV의 편차(E)를 산출한 후 PID 제어 동작을 수행한다. 그 결과인 조작치(MV)를 PWM 블록에 제공하여 실질적으로 DC 서보 모터를 구동하는 H-bridge 회로를 구동한다. 또한 FPGA 내부의 SV, PV, E, MV를 오실로스코프로 계측하기 위해 DAC 인터페이스 블록을 첨가하여 외부 디지털 아날로그 변환기(DAC)를 제어 하였다.

#### 1. 서 론

DC 서보 모터의 제어 방식중 PID형이 84.5%, 고급 PID(Advanced PID)형이 6.8%, 현대제어형이 1.5%, AI형이 0.6% 및 수동제어가 6.6%로 PID형과 고급형 PID형을 합해 90%를 초과하고, 더욱이 수동제어 부분을 제외하면 PID를 중심으로 하는고전제어가 전체의 97.5%를 점유하고 있다. 이처럼 긴 역사를 가진 PID 제어도 보다 고성능을 추구하기 위해 디지털 PID 제어방식으로 전환되고 있다.

최근 디지털 논리회로의 고집적화로 디지털 논리회로 분야가 많은 발전을 가져왔고, 시스템 온 칩(SoC)이나 IP(Intellectual Property)에 대한 많은 관심 속에 비메모리 분야에 대한 연구가활발히 진행되고 있어 VHDL을 이용한 대용량의 CPLD나 FPGA로 설계자의 의도에 따라 최적의 시스템을 설계하는 것이용이 해졌다. 또한 규모가 큰 시스템을 고성능, 저비용의 작은 규모의 시스템으로 설계하는 것이 가능해졌다. 이에 따라 FPGA를 이용해 하나의 Chip으로 DC 서보모터의 속도제어 시스템을 구현하였다. 이를 위해 VHDL을 이용한 Top-down 방식으로 여러기능의 블록을 구성하고, 블록 간을 유기적으로 연결한 디지털 로직을 구현하여 전반적인 시스템의 최적 제어가 가능하게되었다.

본 논문에서는 DC 서보 모터의 속도 제어 시스템을 5개의 블록으로 설계하고 블록간을 유기적으로 연결하여 하나의 FPGA로 구성하였다. 각 기능들은 Xilinx ISE, Synplify pro, Modelsim을 이용하여 VHDL로 프로그램하고 합성, 구현, 시뮬레이션을 하였으며 FPGA로 구현하기 위하여 Xilinx사의 10만 게이트인 XC2S100-5TQ 144C를 이용하여 로직을 구현하였다.

### 저자 소개

\*박인수: (주)이씨엠 연구개발 팀장 \*김정옥: (주)이씨엠 전략기획부 이사 \*\*박광현: 충주대학교 전자통신과 정교수

\*\*\*Khalifa Eltayeb kh Mustafa : 말레이시아 공과대학 박사과정

본 연구는 충북테크노파크 (맞춤형과제 "인휠 모터 기반의 미니 전기차 제어시스템 개발", 주관기업 (주) 이씨엠) 지원에 의한 것입니다. 설계된 FPGA를 이용한 DC 서보 모터의 속도제어 시스템과 32bit의 내부구조에 20 MHz의 클럭 주파수로 구동하는 HITACHI사의 H8S/2148를 이용한 속도제어 시스템의 성능을 비교 평가하여 본 논문에서 구현한 시스템이 우수성함을 입증하고 자 한다.

### 2. 본 론

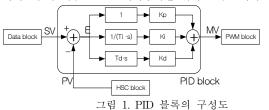

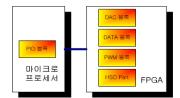

FPGA에 내부에 구현된 블록은 크게 5개로 나누어진다. 시스템 유저로부터 운전목표치와 이득 값을 입력받아 해당 블록에 값을 전달해주는 데이터 통신 블록과 오실로스코프로 설정치(SV), 프로세서치(PV), 편차(E), 조작치(MV)를 측정하기 위해외부 디지털/아날로그 변환기(DAC)를 제어할 DAC 인터페이스블록과 플랜트인 DC 서보모터에서 출력되는 2 채널의 90° 위상차의 펄스를 고속으로 카운트 하여 속도를 측정하는 HSC 블록과 데이터 블록의 설정치와 HSC 블록의 프로세서치의 편차(E)를 PID 제어방식으로 없도록 하여 설정치와 프로세서치가 일치하게 만드는 PID 블록 그리고 PID 블록의 조작량(MV)을 처리하여 H-bridge 회로를 구동하는 PWM 블록으로 구성된다.

## 2.1 PID 블록 (PID Block)

PID 제어를 디지털 화하여 VHDL로 프로그래밍을 하였다. SV값을 컴퓨터로부터 호스트 통신을 통해 받고 HSC 블록을 통해 PV을 얻어 E를 구하고 PID 제어동작을 취해 MV값을 얻어 PWM 블록에 보내면 H-bridge를 적절하게 구동하여 이러한 제어시스템의 핵심은 PID 제어동작을 취하는 부분이다.

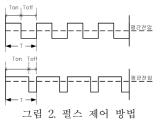

## 2.2 펄스폭변조 블록 (PWM Block)

그림 2과 같이 모터에 인가되는 전압을 ON/OFF 시켜서 모터에 인가되는 평균전압을 변화시킨다. ON 시간이 길수록 모터에 가 해지는 평균전압이 그림 2의 두 번째와 같이 변하게 된다.

## 2.4 고속카운터 블록 (HSC Block)

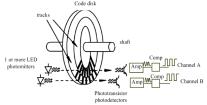

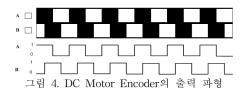

DC 서보 모터는 그림 3과 그림 4처럼 90° 위상차의 펄스 신호를 2 채널에서 출력하며 속도가 증가 할수록 일정시간동안 나오는 Pulse의 수는 증가하게 된다. 본 논문에서 사용한 DC 서보 모터 는 432 R/P의 출력을 내보내며 3900 RPM의 속도로 회전 할 수 있다.

그림 3. DC 모터의 엔코더

2.5 데이터 통신 블록 (DATA Block)

사용자가 컴퓨터에서 PID 제어에 필요한 설정치와 P제어 이득 값, I제어 이득값, D제어 이득값을 설정하거나 SV, PV, E, MV 및 수행되는 과정 확인 할 수 있는 변수를 모니터링을 하고 모니터링한 값을 그래프로 그리는 화면이다.

그림 5. 컴퓨터상에서 설정 및 모니터링

2.6 디지털/아날로그 변환기 인터페이스 블록

#### (DAC Interface Block)

PID 제어에 사용되는 설정치, 프로세서치, 편차, 조작치들을 외부에서 실시간으로 확인하기 위해서 오실로스코프로 사용하여 계측하여야 한다. 데이터블록에서는 최대 100ms 마다 계측을 하기때문에 계측되는 값이나 그래프를 신뢰하기 힘들다. 본 논문에서는 DAC 인터페이스 블록을 이용하여 외부에 있는 8 비트 4 채널 DAC인 AD7226을 구동하여 DAC 출력 값을 500 MHz의 오실로스코프를 사용하여 계측하였다.

## 2.7 실험 및 결과

그림 6은 하나의 FPGA를 이용하여 DC 서보 모터의 속도제어 시스템을 구현한 것이다. 다시말해 PID, HSC, PWM, 데이터통신, DAC 인터페이스 블록을 FPGA만을 이용하여 구현한 것이다. 그리고 그림 7은 PID블럭을 마이크로프로세서에서 구현하고나머지 블록을 FPGA에서 구현한 것이다. 따라서 HSC, PWM, 데이터 통신, DAC 인터페이스 블록은 동일한 동작을 수행한다. 또한 PID 블록도 구현대상인 FPGA나 마이크로프로세서의 차이일 뿐 제어 동작은 동일하다.

그림 6. FPGA만을 이용한 시스템

그림 7. FPGA와 마이크로프로세서를 이용한 시스템

#### 3. 결 론

FPGA를 이용하여 DC 서보 모터의 속도제어 시스템을 구현하면 하나의 칩으로 PID(Proportional,Integral,Derivative), HSC(High Speed Counter), PWM(Pulse Width Modulation), DAC(Digital Analog Converter) 인터페이스, 데이터 통신 모든 기능이 2만 게이트의 규모로 구현이 가능하며 또한 이후 필요한 기능의 추가가 용이하다. 따라서 제어 시스템의 규모가 현저하게 작아지고, 시스템에 적용 시 간편하게 구현할 수 있다. 또한 경제적인 측면에서 본 시스템을 ASIC()화하면 주변 펌웨어가 필요한 마이크로프로세서를 이용한 시스템보다 경제적이다.

시스템의 HSC 블록을 이용하면 DC 서보 모터의 엔코더로부터 입력되는 2 채널의 펄스 신호를 이용하여 2상 4체배하여 정밀하게 정·역 카운트를 할 수 있다. 그리고 PWM 블록을 이용하면 DC 서보 모터를 구동하는 H-bridge에 필요한 4개의 PWM 신호를 4000 샘플링으로 만들 수 기능이 있다. 또한 SV, PID 제어이득을 FPGA의 외부 IO PIN을 이용하게 간단하게 입력 받을수 있어 시스템에 적용할 때 간편하게 정밀한 제어를 구현 할수 있다.

#### [참 고 문 헌]

- [1] 티니코시 킨지, "모터의 구조", 세화, 1997.

- [2] 성수광, "PID controllers and Automatics Tuning", 영진.com, 1999.

- [3] 오성권, "퍼지모델 및 제어 시스템", 내하출판사, pp 213-490, 2002.

- [4] 송재훈, "A Design of Flag Based Wrapped Core Linking Module for Hierarchical SoC Test Access", 대한전자공학회논문지 SD(Journal of the Institute of Electronics Engineers of Korea SD) 2003,1 v.040, n.001, pp.52-60 1229-6368

- [5] 김재철, "ISE를 이용한 VHDL 및 FPGA 실습", 흥릉과학 출판사, 2003.

- [6] 박주성, "FPGA를 이용한 ASIC 설계 실습", 흥릉과학출판 사, 1997.

- [7] 허재동, "시퀀스 제어용 32비트 마이크로프로세서설계에 관한 연구", 석사학위논문. 2002.

- [8] 이도향, 양오, "FPGA를 이용한 다기능 고속 카운터 구현 에 관한 연구", 대한전기학회, 2003.

- [9] Ying-Yu Tzou, "FPGA Realization of Space-Vector PWM control IC for Three-Phase PWM Inverters", IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 12, NO. 6, NOVEMBER 1997.

- [10] Xilnix, "XC2S100 User's guide", 2003.

- [11] Hitachi, "H8S/2148 User's guide", 2002.

- [12] 양 오, "신경회로망을 이용한 제어 시스템의 설계에 관한 연구", 박사 학위논문, 1996.

- [13] Kenji Tamaki, "Micorprocessor-Based Bobust Control of a DC Servo Motor", IEEE CONTROL SYSTEM Magazine, October 1986