# A New Four Level Half-bridge Converter

In-Ho Cho, Kang-Hyun Yi, Kyu-Min Cho, Young-Do Kim and Gun-Woo Moon

Department of Electrical Engineering and Computer Science, KAIST 373-1 Guseong-Dong, Yuseong-Gu Daejeon 305-701, KOREA

# Abstract

A new four level half-bridge converter is proposed in this paper. Compared to a conventional half-bridge converter and an asymmetric half-bridge converter, the proposed converter has less stress on power switching components and have smaller output inductor. Zero-voltage-switching condition is also achieved with the proposed converter. The operational principle, DC conversion ratio and ZVS analysis are presented. Experimental results are demonstrated to verify the feasibility and advantages of the new topologies.

# 1. Introduction

As function of computer and telecommunication devices are advanced, requirements for converters used in server power, PC power and telecommunication are getting more complicated. To meet these rigorous requirements (such as zero-voltage switching, high power density, high efficiency and low EMI property) various control techniques and many new topologies have been suggested. In half-bridge topologies, widely used in medium power application, an asymmetric duty cycle control technique has been recognized as a candidate for high-density and high-efficiency dc/dc power converter applications due to its zero-voltageswitching (ZVS) condition. However, in general, it also suffer from these limitations: 1) Duty cycle is limit under to 0<D<0.5 and it is far more restricted under wide input voltage range; 2) Voltage stress on the output rectifier is unbalanced due to asymmetric switching time of the main switches; 3) DC offset current is showed, it reduce the utilization of the transformer and it leads to increase the current rating of the main switches. Some of these limitations can be overcome by adopting two-transformer to enlarge the duty cycle[2] or adopting one more switch on the rectifier side[3]. However, in these cases, transformer should be doubled or control technique becomes difficult.

In the proposed converter, voltage stress on the output rectifier is equally distributed and it has no dc offset current. It also achieve good zero-voltage-switching condition in all switches and output inductor size can be reduced. The operational principles, analysis and experimental results are presented to confirm the validity of the proposed converter.

# 2. Operation Principle

### 2.1 Circuit configuration

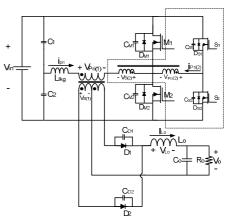

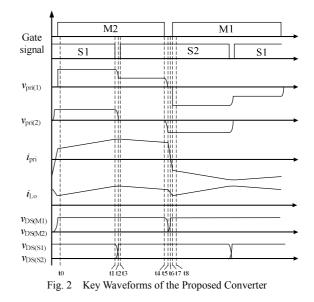

Fig.1 shows the circuit diagram of the proposed converter and Fig.2 is its key waveforms in steady state. A small transformer and small two switches are connected to the conventional half-bridge circuit. Compare to an asymmetric half-bridge converter, the proposed converter needs one more transformer and two more switches in the primary side. However, when considering the size and efficiency, the proposed converter shows better performance.

Fig. 1 A New Four Level Half Bridge Converter

The transformer size can be reduced compare to an asymmetric half-bridge converter because it has no DC offset current with its symmetric switching control and the size of the added components is smaller than the main components. Also the output filter inductor size is reduced because the frequency shown at output filter of the proposed converter is twice faster than the one in an asymmetric half-bridge converter.

## 2.2 Operation Principle

For the convenient analysis of the steady state operation several assumptions are made as follows;

a) All parasitic components except for the leakage inductor are neglected,

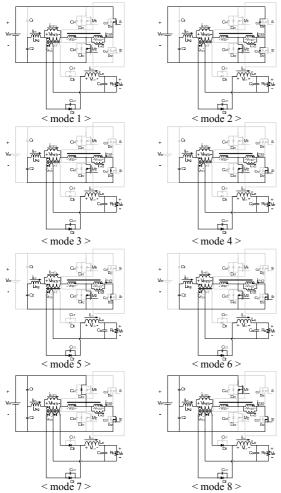

Fig. 3 Equivalent circuit of the proposed converter

- b) The switches M1, M2, S1 and S2 are ideal except for their output capacitors and body diodes,

- c) The capacitors, C1 and C2, are large enough to be considered as a constant voltage source (1/2)Vs,

- d) Turn ratio of the main transformer is n1=N1/N2 and n2=Ns1/Ns2 for the sub transformer.

- e) The primary current is constant during the very short period;  $t_1 \sim t_2$ ,  $t_2 \sim t_3$  and  $t_4 \sim t_5$

**Mode**  $1(t_0 \sim t_1)$ : Mode 1 begins when the commutation of the secondary rectifier diode is completed. Input energy is transferred into the secondary side in this mode by main-switch M2, sub-switch S1 and transformers. At this time, the larger voltage is applied to the main transformer than the voltage in asymmetric half-bridge converter so it helps to reduce the conduction loss in primary side. The transformer voltage and primary/secondary current are given as:

$$V_{\rho r(2)} = V_{s}, \qquad V_{\rho r(1)} = \frac{1}{2} V_{s} + \frac{1}{n_{2}} V_{\rho r(2)}$$

(1)

$$i_{\rho n}(t) = \frac{1}{n_1} i_{\rho}(t) \tag{2}$$

$$i_{o}(t) = \frac{\left(V_{S(1)} - V_{o}\right)}{L_{o}} + i(t_{o}), \quad \left(V_{S(1)} > V_{o}\right)$$

(3)

**Mode 2(t<sub>1</sub>~t<sub>2</sub>) :** At time t<sub>1</sub>, sub-switch S1 is turned off and its output capacitor  $C_{S1}$  is charged from 0V to  $V_{in}$  while the output capacitor of the sub-switch S2 is discharged form  $V_{in}$  to 0V. Because the energy is large enough to charge / discharge, the capacitor voltage of sub-switches is linearly increasing and decreasing. Also the sub-transformer voltage is decrease to zero along with the capacitor voltage  $V_{Cs2}$ .

$$V_{C_{11}} = \frac{\frac{1}{n} i_{\rho\sigma}(t_1)}{C_{11} + C_{22}} (t - t_1)$$

(4)

$$V_{C_{x2}} = V_{pri(2)} = V_{in} - \frac{\frac{1}{n} i_{pri}(t_1)}{C_{S1} + C_{S2}} (t - t_1)$$

(5)

**Mode 3(t<sub>2</sub>~t<sub>3</sub>) :** After V<sub>Cs2</sub> is discharged to 0V in mode2(V<sub>Cs1</sub> is charged to V<sub>in</sub>), the reflected primary current  $i_{pri(2)}$  flows through the body diode of the sub-switch S2. At this time V<sub>Cs2</sub> and the sub-transformer voltage is sustained to 0V and the main-transformer primary voltage is V<sub>in</sub>/2.

**Mode 4(t<sub>3</sub>~t<sub>4</sub>) :** The sub-switch S2 is turned on at time  $t_3$ . Since  $V_{Cs2}$  is 0V, S2 is turned on under ZVS condition. In this mode primary current decrease following the output inductor current. The primary current  $i_{pri}$  is expressed as follows;

$$i_{\rho n}(t) = \frac{1}{n_1} i_o(t)$$

(6)

$$i_o(t) = \frac{\left(V_{S(1)} - V_o\right)}{L_o} + i(t_s), \quad \left(V_{S(1)} \land V_o\right)$$

$$\tag{7}$$

**Mode 5**( $t_4$ - $t_5$ ) : The main-switch M2 is turn-off at the beginning of this mode. The voltage of the output capacitor,  $C_{M2}$ , is linearly charged from 0V and the voltage of  $C_{M1}$  is linearly discharged from  $V_{in}$  at the same time by the large energy of output inductance. This mode continues until the time when the primary voltage of the transformer reaches to 0V.

$$V_{C_{u2}}(t) = \frac{i_{\rho r}(t_{4}) + \frac{1}{n_{2}} i_{\rho \rho}(t_{4})}{C_{M1} + C_{M2}}(t - t_{4})$$

(8)

$$V_{pri(1)}(t) = \frac{V_{in}}{2} - \left( V_{C_{W2}}(t) + \frac{1}{n_2} V_{C_{W2}}(t) \right)$$

(9)

**Mode**  $6(t_5 \sim t_6)$ : After the primary voltage of the main transformer reaches to 0V, the voltage of main-switch M2 increases in manner of resonance between L<sub>lkg</sub> and 'C<sub>M1</sub>+ C<sub>M2</sub>. 'The voltage of M2 and the primary current are expressed as follows;

$$V_{C_{M2}}(t) = \left(i_{pn}(t_5) + \frac{1}{n_2}i_{pn}(t_5)\right)\sqrt{\frac{L_{ikg}}{C_{M1} + C_{M2}}}\sin\left(\sqrt{\frac{L_{ikg}}{C_{M1} + C_{M2}}}t\right) + V_{C_{M2}}(t_5)$$

(10)

$$i_{\rho\sigma}(t) = i_{\rho\sigma}(t_{5})\cos\left(\sqrt{\frac{L_{ling}}{C_{M1} + C_{M2}}}t\right)$$

(11)

In the secondary side, both rectifier diodes are conducted and commutation of the two diodes, D1 and D2, begin. This mode ends when the switch M1 voltage discharges to 0V.

**Mode**  $7(t_6 - t_7)$ : The primary current flows through the mainswitch M1 whose voltage discharges completely in a previous mode. After the direction of the primary current is changed, the current flows through the body diode of M1. The primary current is expressed as;

$${}_{\rho\sigma}(t) = -\frac{\frac{1}{2}V_{in} + \frac{1}{n_2}V_{in}}{L_{u\alpha}}(t - t_6) + i_{\rho\sigma}(t_6)$$

(12)

This mode continues until following condition is satisfied;

$$n_{t'\rho\sigma}(t) = i_{Lo}(t) \tag{13}$$

**Mode**  $8(t_7 - t_8)$ : When the reflected primary current reaches output inductor current, the secondary rectifier diodes finish its commutation. D2 is turned off and the secondary current flows through D1. Input energy is transfer to secondary side. The operation is similar to that of mode1.

## 3. Analysis of the Proposed Converter

In this section, DC conversion ratio, ZVS condition, offset of magnetizing current and output inductance are presented.

## A. DC conversion ratio

The DC conversion ratio of the proposed converter can be expressed as follows;

$$\frac{V_o}{V_{in}} = \frac{2}{n_1} \times \left(\frac{D_{eff}}{n_2} + \frac{1}{4}\right)$$

(14)

$(D_{eff}: the duration of mode1)$

The DC conversion ratio of the proposed converter is first order equation, so that the variation depends on the input voltage variation is linearly changed.

### **B. ZVS condition**

The proposed converter is able to have ZVS action(for mainswitches) when it meets this condition:

$$\frac{1}{2}(C_{M1}+C_{M2})\left(V_{in}-\frac{\frac{1}{2}V_{in}}{1+\frac{1}{n_2}}\right) \leq \frac{1}{2}L_{iig}(i_{jni(1)}+\frac{i_{jni(1)}}{n_2})^2$$

(15)

The sub-switches are well achieved ZVS condition using output inductor energy. For the main-switches, the output inductor is concerned until the time when main-transformer secondary side is shorted. Also the current which is reflected by the sub-transformer helps for ZVS of main switches.

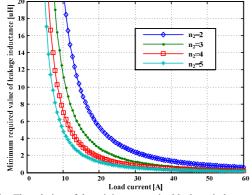

Fig. 4 The relation of the minimum required leakage inductance and load current(at 700W, Vo=12V spec.)

Fig. 4 shows the required leakage inductance on every load current condition. As load current increase, required leakage inductance for ZVS is decrease. The minimum required leakage inductance is also influenced by sub-transformer turn ratio. In a larger turn ratio, the better ZVS condition is achieved.

#### C. DC offset of magnetizing current

The DC offset of magnetizing current can be calculated by applying current-second law to  $C_2$ . It can be expressed as follows:

$$D_{eff}\left(I_{Lm} + \frac{I_o}{n_1}\right) = D_{eff}\left(-I_{Lm} + \frac{I_o}{n_1}\right)$$

$$\therefore I_{Lm,DCoffset} = 0$$

(16)

# **D.** Output inductance

In a conventional DC/DC converter, the output inductance can be calculated by following equation;

$$L_{o} = \frac{V_{Lo}}{\Delta I_{o}} DT$$

(17)

For the proposed converter, above equation is represented as:

$$L_{o} = \frac{\left[\frac{1}{2}V_{in} + \frac{1}{n_{2}}V_{in}\right]}{\Delta I_{o}} - V_{o} D_{eff} \frac{T}{2}$$

$$\tag{18}$$

In a proposed converter, the frequency shown at the output filter inductor is twice higher than the switching frequency of the DC/DC converter..

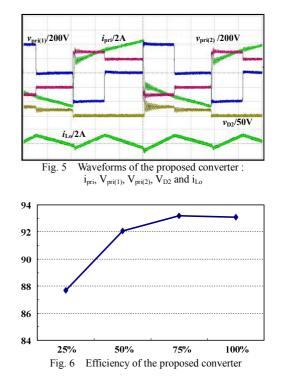

## 4. Experimental Results

To verify the operation of the proposed converter, prototype circuit has been designed with following specifications : Input

voltage : 400V(330V~400V). Output voltage/current : 12V/58A. Switching frequency : 86kHz. The magnetic cores used for the main transformer is EI3329 and for the sub-transformer is EI3026. The switches used in the primary side are SPP20N60C3. IRFB3077 switches are used for the synchronous rectifier switches in the secondary side. As shown in fig 5, the voltage of the main transformer is consisted of four different voltage level and there is no dc offset current in the primary current. Higher frequency of the output inductor current and ZVS switching characteristics are also the merits of the proposed converter.

#### 5. Conclusion

A new four level half-bridge converter is presented and analyzed. Even though the proposed circuit needs additional components, one small transformer and two small switches, it has low conduction loss, good ZVS condition and small output filter inductance. Furthermore, no DC offset characteristics helps to reduce the transformer size and distributes voltage / current stress symmetrically. The experimental results of the proposed converter prove the good performance of a new four level half-bridge converter.

#### Reference

[1] P. Imbertson and N. Mohan, "Asymmetrical Duty Cycle Permits Zero Switching Loss in PWM Circuits with No Conduction Loss Penalty," IEEE Trans Industry Applications, vol. 29, no. 1, Jan/Feb. 1993, pp.121-125

[2] YH Leu, TM Chen and CL Chen, "Analysis and Design of the Two-Transformer Asymmetrical Half-Bridge Converter," Industrial Electronics Society, 2005. IECON. 32<sup>nd</sup>

[3] KM Cho, "A New-Half Bridge Converter without DC offset of magnetizing current," KIPE conference 2007, pp.147-149

[4] W Song, B Lehman, "Dual-bridge DC-DC converter : a new topology characterized with no deadtime operation," Power Electronics, IEEE Transactions on, 2004.

[5] GB Koo, GW Moon, MJ Youn, "Analysis and design of phase shift full bridge converter with series-connected two transformers," Power Electronics, IEEE Transactions on, 2004, 19, pp. 411-419