# ESD Protection Circuits with Low-Voltage Triggered SCR for RF Applications

\*김산홍, \*박재영, \*김택수 \*동부 하이텍 TE센터 DE팀

e-mail: sanhong.kim@dongbu.com, jaeyoung.park@dongbu.com

# ESD Protection Circuits with Low-Voltage Triggered SCR for RF Applications

\*San-Hong Kim, \*Jae-Young Park, and \*Taek-Soo Kim \*DE Team, TE Center, Dongbu HiTek Co., Ltd.

#### Abstract

An Electrostatic discharge (ESD) protection has been a very important reliability issue in microelectronics, especially for RF (Radio Frequency) integrated circuits (ICs). This paper reviews design and analysis of on-chip ESD (electrostatic discharge) protection circuits for RF applications. Key issues in RF ESD protection, design methods, and RF ESD protection solutions are discussed.

#### I. 서론

전자 제품에서 ESD (Electrostatic Discharge) 문제의 중요성은 점점 커지고 있지만 그 해결 방안은 점점더 어려워지고 있다 [1]. LDD (Lightly Doped Drain), Silicide 등 공정 기술의 발전은 ESD 보호 회로에 악영향을 주는 방향으로 발전하고 있기 때문에 적절한 ESD 보호 회로를 구성하는 것이 어렵다. 또한 제품군에 따라 요구하는 스펙이 달라 각각 다른 ESD 보호 회로를 제공하여야만 하는 문제도 추가로 발생한다[2]. 특히 RF (Radio Frequency) IC의 경우 동작 주파수대가 수 GHz이며, 옥사이드 항복 전압이 낮기에 일반로직 IC에 비해 ESD 문제 해결이 더욱 어렵다[3].

이와 같은 문제를 해결하기 위해 본 논문에서는 RF 제품을 위한 ESD의 고려사항에 대해 살펴 본 후, RF 제품을 위한 ESD 보호회로의 설계 방법에 대해 논한다.

## II. 본론

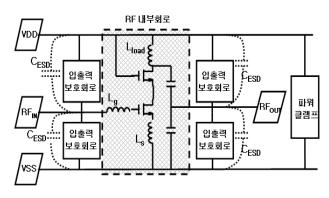

2.1. RF 제품을 위한 ESD 보호회로의 고려사항 RF IC에 사용되는 ESD 보호회로의 구성은 그림1과 같다. 입출력 ESD 보호를 위해 입출력 단과 VSS 사이, 입출력 단과 VDD 사이에 입출력 보호회로를 배치한다. 또한 파워 단 간의 ESD 보호를 위해, 파워 클램프를 배치하여 전체 ESD 보호회로를 구성한다.

그림 1. RF IC을 위한 ESD 보호회로의 구성

이와 같은 ESD 보호회로의 구성은 일반적인 구성이며, 로직 IC에 문제없이 적용할 수 있다. 하지만 RF IC의 경우, 입출력 ESD 보호회로의 기생 커패시턴스에 의해 전체 회로의 성능이 크게 감소되며, 결국 오동작을 일으키게 된다. 이러한 문제 때문에 RF 제품을 위한 ESD 보호회로는 0.2pF 이하의 작은 기생 커패시턴스를 갖게 설계하여야 한다. 하지만 많은 전류를 감당해야 하는 ESD 보호회로의 특성 상 큰 면적을 가질수밖에 없고, 이에 따라 작은 기생 커패시턴스를 갖는 ESD 보호회로를 설계하는 것은 어려운 일이다.

또한 본 논문에서 사용한 130 nm RF 공정의 게이트 옥사이드의 두께는 2.5 nm 정도이며 게이트-옥사이드 항복 전압이 약 8V로, 입출력 ESD 보호회로의트리거링 전압은 8V 미만으로 설계되어야 한다.

#### 2.2. RF 제품을 위한 ESD 보호회로의 설계 방법

로직 IC의 경우 ESD 보호를 위해 게이트를 그라운 드와 묶은 grounded-gate NMOS (ggNMOS) 가 주로 사용된다. 이 소자는 트리거링 전압이 낮지만, 큰 면적 을 가지며 그에 따라 큰 기생 커패시턴스를 가져 RF 제품을 위한 ESD 보호 회로에 적합하지 않다. 그렇기 때문에 RF 제품을 위한 ESD 보호회로에는 SCR (Silicon Controlled Rectifier) 이 사용된다. SCR은 PNPN 구조를 이용하기 때문에 작은 면적에도 많은 전류를 감당할 수 있고, 따라서 기생 커패시턴스 측면 에서도 우수하다. 하지만 SCR 역시 RF 제품을 위한 ESD 보호회로로 사용하기에는 문제가 있는데, 이것은 높은 트리거링 전압 때문이다. 일반적인 CMOS 공정 에서 제작되는 SCR의 경우 10V 이상의 높은 트리거 링 전압을 갖고, 이것은 입력 회로의 게이트-옥사이드 항복을 일으킬 수 있다. 그러므로 이 SCR의 트리거링 전압을 낮추어야 하며, 동시에 최대한 작은 커패시턴 스를 가지도록 ESD 보호 회로를 설계하여야 한다.

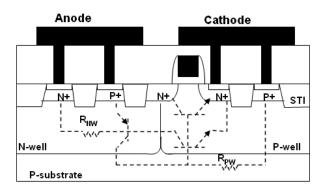

그림 2는 이와 같은 요구를 만족하는 SCR 구조 (Low-Voltage Triggered SCR, LVTSCR)로 130 nm RF CMOS 공정에서 제작되었다[3]. 작은 기생 커패시 턴스를 갖기 위하여 SCR의 구조를 유지하면서, 낮은 트리거링 전압을 얻기 위하여 ggNMOS 구조를 SCR 내에 적용한 ESD 보호 소자이다. 입력 단을 통해 ESD 펄스가 들어오면, 내부에 적용된 NMOS가 낮은 전압에서 트리거링 되고, 곧 SCR을 동작시켜 많은 전류를 흘릴 수 있게 만든 구조이다. 이것은 작은 커패시턴스를 가지면서 트리거링 전압 역시 낮아 RF 제품을 위한 ESD 보호 회로에 적합하다. 표 1에서 130 nm RF CMOS 공정에서 제작된 ggNMOS, SCR, LVTSCR의 특성을 비교하였다.

그림 2. 130 nm RF CMOS 공정에서 제작된 LVTSCR 구조도

표 1. 130 nm RF CMOS 공정에서 제작된 ggNMOS, SCR, LVTSCR의 특성 비교

|                  | ggNMOS | SCR  | LVTSCR |

|------------------|--------|------|--------|

| Capacitance [pF] | 1.5    | 0.2  | 0.2    |

| 트리거링 전압 [V]      | 6.2    | 12.8 | 7.2    |

| 이차 항복전류 [A]      | 2.9    | 2.7  | 2.6    |

## Ⅲ. 결론 및 향후계획

RF 제품을 위한 ESD의 고려사항에 대해 살펴 본후, 130 nm RF CMOS 공정을 이용하여 RF 제품을 위한 ESD 보호회로를 설계하고 기존 보호회로와 비교하였다. 설계된 RF 제품을 위한 ESD 보호회로는 7.2V의 낮은 트리거링 전압과 0.2pF의 기생 커패시터를 가져, 수 GHz 대역의 RF 제품의 요구를 충분히 만족한다. 수 십 GHz 대의 RF 제품의 요구를 만족하기 위해서는 더 작은 기생 커패시턴스를 갖는 ESD 보호회로 필요하며, SCR을 변형한 구조에 대해 연구 중이다.

\* 본 논문은 지식경제부 하의 차세대 성장 동력사업의 후원으로 연구되었습니다.

#### 참고문헌

- [1] A. Ameraskera and C. Duvvury, ESD in Silicon Integrated Circuits, John Wiley & Sons Ltd, West Sussex, England, 1995.

- [2] Wang, A.Z., Feng, H.G., and Stine, J., "On-chip ESD protection design for integrated circuits: an overview for IC designers," Microelectronics Journal, v.32 no.9, 2001, pp.733-747.

- [3] Wang, A.Z., "A review on RF ESD protection design," IEEE Trans. Electron Devices, vol.52 no.7, 2005, pp.1304–1311.