# UWB용 Frequency Synthesizer와 Sub-Band Generator의 설계

A Design of Frequency Synthesizer and Sub-Band Generator for UWB

박준성\*, 남 철\*\*, 오환술\*\*\*, 천정인\*\*\*\*, 이강윤\*\*\*\*\*

건국대학교 석사과정\*, 건국대학교 박사과정\*\*, 건국대학교 교수\*\*\*, 삼성전기\*\*\*\*, 건국대학교 교수\*\*\*\*

Key Words: UWB, Frequency Synthesizer, SSB, Mixer

목 치

- I. 서론

- II. 본론

- 1. 구조

- 2. 구성 블록

- 3. 모의 실험 결과

- 4. 레이아웃 결과

- Ⅲ. 결론

# │. 서 론

UWB용 송수신기의 설계 시 전력 소모 및 면적, 9.5ns의 빠른 채널 스위칭 시간이 중요한 성능 파라미터로 요구된다. 본 논문에서는 UWB용 송수신기에서 LO 주파수를 생성해주 는 Frequency Synthesizer 및 Sub-Band Generator의 설계 결과를 보여주고 있다. 빠른 채널 스위칭 시간을 만족하기 위해서 1개의 PLL과 2개의 SSB mixer로 구성하였으며, 전류 소모 및 면적을 최소화 하도록 설계하였다. 또한, 효과적인 Frequency Planning을 통하여, 6336MHz의 단일 주파수를 입 력으로 받아 UWB Band Group1에 해당하는 3432MHz, 3960MHz, 4488MHz의 중심 주파수를 발생시키는 Sub-Band Generator를 설계하였다. VCO의 튜닝 Range는 1GHz이며, 6336MHz의 출력 주파수에서의 Phase Noise는 1MHz Offset 에서 -121dBc/Hz 이었다. UWB용 Frequency Synthesizer 및 Sub-Band Generator는 IBM 0.13um 공정으로 설계하였으며, 전체 Chip 면적은 3.3mm x 3mm이다. 전력 소모는 1.5V 의 공급 전원에서 190mW이다.

# Ⅱ. 본 론

#### 1. 구 조

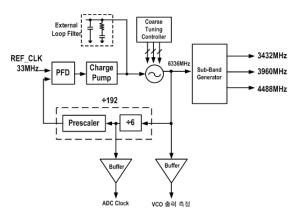

<그림 1>은 주파수 합성기의 구조를 보여주고 있다. 설계 된 주파수 합성기는 33MHz의 reference clock을 외부에서 받 아서 안정적인 6336MHz의 주파수를 발생시킨다. PLL은 LC voltage-controlled oscillator(VCO)와 전체 192의 분주비를 갖는 주파수 분주기, phase frequency detector(PFD), charge pump로 구성된다. Loop Filter는 면적을 고려하여 외부에서 구현 가능하도록 설계 하였다.

<그림 1>의 구조는 baseband단 모뎀의 ADC에 clock을 공급할 수 있다. 이에 따라, baseband단 모뎀에서는 ADC에

<그림 1> Frequency Synthesizer의 구조

clock을 공급하기 위한 PLL을 제거할 수 있다.

주파수 분주기의 6분주기는 UWB baseband단 모뎀의 ADC 에 1.056GHz의 clock을 공급하며, duty cycle을 50%로 맞추기 위해 3분주기 다음에 2분주기가 오는 구조로 구성하였다. VCO의 출력 주파수인 6336MHz는 3분주기에 의하여 2112MHz로 분주되고, 이어서 2분주기에 의하여 1056MHz로 분주된다.

2개의 SSB Mixer는 UWB Band Group1에 해당하는 3개의 주파수인 3432MHz, 3960MHz, 4488MHz의 중심 주파수를 발 생시킨다.

#### 2. 구성 블록

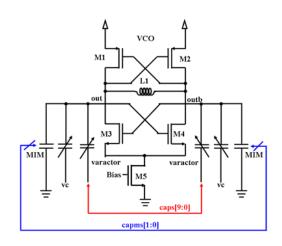

<그림2>는 phase noise 특성을 만족시키기 위한 LC 타입 의 VCO의 구조를 보여주고 있다. 6336MHz의 높은 중심 주 파수를 갖는 VCO는 Q값을 높이기 위한 고정 MIM 커패시터 와 MIM coarse 튜닝 커패시터, varactor를 사용한 커패시터 bank, 그리고 Multi-level varactor 튜닝 커패시터로 구성된

VCO는 6336MHz의 높은 중심 주파수를 갖기 때문에, VCO의 커패시터 값은 매우 작다. 최대한 큰 커패시턴스와 작은 인덕턴스 값을 사용하는 것이 VCO의 튜닝 range를 넓 히는데 있어서 큰 이슈이다. 이에 따라, 인덕터는 좋은 Q값 을 갖기 위해서 0.6nH의 값으로 선택했다.

<그림 2> VCO의 구조

작은 커패시턴스 변화량을 갖는 VCO의 튜닝을 위해서, MIM 커패시턴스와 스위치로 구성된 일반적인 coarse 튜닝 커패시 턴스는 본 논문의 VCO에 사용할 수 없다. 이에 따라, MIM 커패시터와 varactor 커패시턴스로 구성된 새로운 coarse 튜 닝 커패시턴스를 사용하였다.

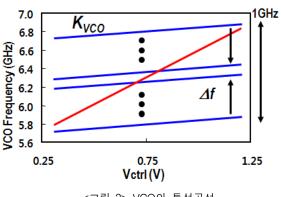

<그림 3> VCO의 특성곡선

MIM 커패시턴스 부분은 CAPMS[1:0]의 2비트에 의하여 조정되며 1GHz의 범위를 커버한다. 세밀한 튜닝을 위한 varactor 커패시턴스 array는 CAPS[9:0]의 10개 비트로 조정 된다.

VCO의 coarse 튜닝은 다음의 단계대로 진행된다. 첫 번째, MIM coarse 튜닝 단계에서 MIM 커패시터는 CAPMS[1:0]의 2개 비트에 의해 조정되며, 넓은 VCO 튜닝 범위를 커버한다. VCO control 전압은 Vctrl은 0.75V이다. 두 번째, varactor 튜닝 커패시턴스 array가 CAPS[9:0]의 10 개 비트로 조정된다. 이는 CAPMS[1:0]에 따른 넓은 튜닝

제안된 coarse 튜닝 기법에 따라 최적화된 LC-VCO의 튜 닝 커패시턴스는 phase noise와 lock time을 최적화시키기 위 해 선택된다.

가격을 커버한다.

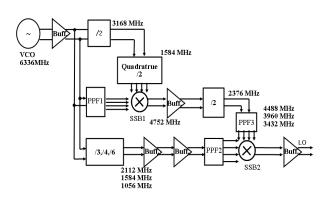

<그림4>는 Sub-Band Generator(SBG)의 구조를 보여주고 있다. VCO로부터 6336MHz의 differential 신호를 받아, 2개 의 SSB mixer와 분주기를 이용하여, 3342MHz, 3960MHz, 4488MHz의 LO 주파수를 발생시킨다. VCO의 출력 신호가 buffer를 통과하여 full-swing level로 증폭이 되면, SBG의 각 블록에 전달된다. PPF(Poly Phase Filter)는 differential 신호를 받아서 quadrature 신호로 변환해준다.

3분주기와 4분주기, 6분주기의 전력 소모는 최소화 하기 위하 여 각 LO 주파수를 발생시킬 때 해당되는 블록만 동작하도 록 설계하였다. 6분주기를 구성하는 2분주기와 3분주기 사이 에는 큰 부하 임피던스를 구동시키기 위해 버퍼를 삽입하였 다.

<그림 4> Sub-Band Generator의 구조

UWB 시스템은 Frequency Synthesizer로부터 quadrature 신호를 출력하도록 요구한다. 이에 따라. SSB Mixer 전 단 에 PPF를 사용하였다. PPF는 up/down conversion mixer를 구동시키기 위한 quadratue 신호를 생성하기 위해 사용하였 다. SSB Mixer를 구동시키기 위해서는 PPF에서 일정 수준 이상의 출력 신호를 내보내야 하며, PPF에서 신호가 감쇄하 는 것을 보상하기 위한 버퍼를 추가함에 따라 전력 소모가 증가하게 된다.

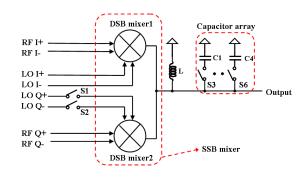

<그림 5> SSB Mixer

UWB system에 사용되는 Frequency Synthesizer의 출력 신호는 UWB 송수신기의 up/down conversion mixer를 위한 local oscillator로 사용되기 때문에 single sideband 신호가 되 어야 한다. SSB Mixer는 2개의 Double-Side Band(DSB) Mixer의 조합으로 구성할 수 있으며, 이는 single sideband 신호를 발생시키는데 사용된다.

본 논문에서는 완전한 differential 구조의 설계를 위해 DSB Mixer는 Gilbert DSB Mixer로 설계하였다. SSB Mixer의 출력 신호는 하모닉 성분에 대한 특성이 좋아야 하며, 큰 전압 스윙을 가져야 한다. 이를 위해, SSB Mixer 출력단에 LC 필터를 삽입하여 공진 주파수를 조정할 수 있도록설계하였다.

공진 주파수인 3432MHz, 3960MHz, 4488MHz는 <그림 5>에서 보여주고 있는 바와 같이, 커패시터와 스위치로 구성된 커패시터 array로 조정이 가능하며 인덕터가 병렬로 연결되어 있다. 하모닉 성분은 SSB Mixer 출력단의 LC 공진 load를 통해 감쇄시킬 수 있다.

#### 3. 모의 실험 결과

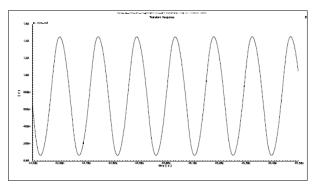

<그림6>은 VCO의 모의 실험 결과를 보여주고 있다. 레이아웃 진행 후에 진행한 Post-Layout Simulation 결과를 보여주고 있다. 튜닝 커패시턴스를 조정하는 비트인 CAPS[9:0]과 CAPMS[1:0]을 중심 주파수 6336MHz의 주파수 신호가 출력되도록 설정한 뒤의 실험 결과이다.

<그림 6> VCO의 Transient 모의 실험 결과

<표 1> VCO의 튜닝 범위 모의 실험 결과

|        | Frequency | CAPS[9:0]  | CAPMS[1:0] |

|--------|-----------|------------|------------|

| Min.   | 5876MHz   | 1111111111 | 11         |

| Center | 6336MHz   | 1000000000 | 10         |

| Max.   | 6891MHz   | 0000000000 | 00         |

| Range  | 1015MHz   |            |            |

<표 1>은 CAPS[9:0]과 CAPMS[1:0]의 설정에 따른 VCO의 튜닝 범위에 대한 모의실험 결과를 보여주고 있다. 최소 주 파수부터 최고 주파수까지 1015MHz의 튜닝 범위를 갖는 것을 알 수 있다.

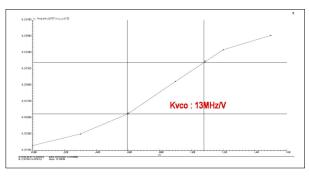

<그림 7> VCO의 K<sub>vco</sub> 모의 실험 결과

<그림 7은> VCO의  $K_{vco}$ 에 대한 모의 실험 결과를 보여주고 있다. VCO 출력 주파수를 중심 주파수인 6336MHz로 설정한 뒤, Control 전압에 따라서 선형적으로 주파수가 증가하는 구간이 13MHz임을 알 수 있다.

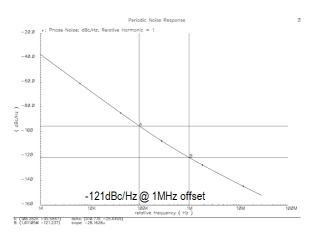

<그림 8> VCO의 Phase Noise 모의 실험 결과

<그림 8>은 VCO의 Phase Noise에 대한 모의 실험 결과를 보여주고 있다. 1MHz offset에서 -121dBc/Hz의 Phase Noise를 갖는 것을 알 수 있다.

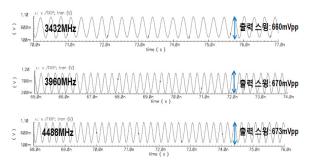

<그림 9> Sub-Band Generator의 Transient 모의 실험 결과

<그림 9>는 Sub-Band Generator의 모의 실험 결과를 보여

주고 있다. 레이아웃 진행 후에 진행한 Post-Layout

Simulation 결과를 보여주고 있다. LO 주파수인 3432MHz,

3960MHz, 4488MHz의 주파수를 갖는 신호가 출력 되는 것을

알 수 있으며, 출력 스윙은 0dBm 이상 출력되는 것을 알 수

있다.

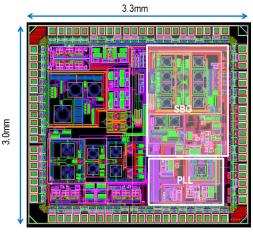

#### 4. 레이아웃 결과

<그림 10>은 레이아웃 결과를 보여주고 있다. IBM 0.13um 공정으로 설계하였으며, 전체 Chip 면적은 3.3mm x 3mm이다.

<그림 10> 칩 사진

# Ⅲ. 결 론

본 논문은 동작 주파수가 3GHz에서 5GHz까지인 UWB용 Frequency Synthesizer에 관한 논문이다. 제안된 주파수 합성기는 PLL 블록과 SBG 블록으로 나눌 수 있다. PLL 블록에서는 VCO의 튜닝 범위를 넓히기 위한 LC-VCO의 새로운 coarse 튜닝 기법이 제안되었다. 또한, 본 논문에서 제안한주파수 합성기의 구조는 baseband단 모뎀의 ADC에 clock을 공급할 수 있다.

본 논문에서는 효과적인 Frequency Planning을 통하여, 6336MHz의 단일 주파수를 입력으로 받아 UWB Band

Group1에 해당하는 3432MHz, 3960MHz, 4488MHz의 중심 주파수를 발생시킬 수 있도록 주파수 합성기를 설계하였다.

VCO의 튜닝 Range는 1GHz이며, 6336MHz의 출력 주파수에서의 Phase Noise는 1MHz Offset에서 -121dB/Hz 이었다. UWB용 Frequency Synthesizer 및 Sub-Band Generator는 IBM 0.13um 공정으로 설계하였으며, 전체 Chip 면적은 3.3mm x 3mm이다. 전력 소모는 1.5V 의 공급 전원에서 190mW이다.

### **Acknowledgement**

본 논문은 지식경제부가 지원하는 국가 반도체 연구개발사업 인 "시스템집적반도체기반기술개발사업(시스템 IC 2010)"을 통해 개발된 결과임을 밝힙니다.

# 참고문헌

- 1. A. Batra, J. Balakrishnan, G.R. Aiello, J.R. Foerster, and A. Dabak, "Design of a multiband OFDM system for realistic UWB channel environments," IEEE Trans. Microw. Theory Tech., vol. 52, no. 9, pp. 2123–2138, Sep. 2004.

- 2. Gerry C. T. Leung and Howard C. Luong. "A 1-V 5.2GHz CMOS Synthesizer for WLAN Applications", IEEE J. Solid-State Circuits, vol. 39, pp 1873–1882, Nov. 2004.

- 3. Kang-Yoon Lee, Hyunchul Ku, Young Beom Kim, "A Fast Switching Low Phase Noise CMOS Frequency Synthesizer with a New Corse Tuning Method for PHS Application," IEICE Trans. FUNDAMENTALS /COMMUN./ELECTRON./INF. & SYST., JUNE. 2005.

- 4. Hyungki Huh, YidoKoo, Kang-Yoon Lee, Yeonkyeong Ok, Sungho Lee, Daehyun Kwon, Jeongwoo Lee, Joonbae Park, Kyeongho Lee, Deong-Kyoon Jeong, Wonchan Kim, "A CMOS Dual-Band Fractional-N Synthesizer with Reference Doubler and Compensated Charge Pump," 2004 IEEE International Solid-State Circuits Conference, pp. 100–101, Feb. 2004.