# AC PDP의 장방전 구조의 구동을 위한 새로운 셀렉티브 리셋파형

송태용, 김동훈, 전원재, 이석현, 인하대학교

# New Selective Reset Waveform for a Large-Sustain-Gap Structure in AC PDPs

Tae-Yong song, Dong-Hun Kim, Won-Jae Kim, Seok-Hyun Lee Inha University

Abstract - A selective reset waveform which can improve the dark room contrast ratio in a large sustain gap structure is suggested in this paper. When conventional selective reset discharge is performed, frequent unexpected misfiring happens because of high Vxb and much quantity of negative wall charge formed on Y electrode during final sustain period. The misfiring between sustain electrode and address electrode can be removed by lowering Vxb value and the misfiring between address electrode and scan electrode can be prevented by applying last sustain pulse of 40us and rectangular pulse of Vscan on Y electrode. When the selective reset waveform has one time reset per 8 subfields, black luminance of 1.55 cd/m2 can be obtained without any misfiring.

#### 1. 서 론

PDP(Plasma Display Panel)는 21세기 디스플레이 시장을 대체할 차세대 디스플레이 장치로서 넓은 시야각, 얇고, 가볍고, 메모리 기능이 있다는 여러 가지 장점들을 가지고 있지만. 향후 LCD 보다 시장우위를 지니기 위해서는 현재 고휘도, 고효율, 저소비전력 등의 쟁점들을 해결하여야 한다. 가장 중요한 문제 중의 하나인 휘도와 효율의 개선을 위해 panel 구조의 개선과 방전 기체의 최적화, 새로운 구동기술 개발 등 다양한 연구가 진행되고 있다. 그 중의 하나가 기존의 negative glow 영역 대신에 positive column의 영역에서 방전하는 장방전 구조이다. 장방전 구조의 sustain 방전을 통한 효율 향상에 관해서는 다양한 연구가 진행되고 있지만,[1] 각각 다른 상태의 셸을 동일하게 해주는 reset 방전에 관한 연구는 미비한 상태이다. 이에 Weber가 발표한 특허를 바탕으로 장방전 구조에서 적용될 수 있는 새로운 리셋 파형을 제한하였다. 하지만 리셋 기간동안 3번의 강 방전이 발생함으로 인한 black 휘도가 너무 높게 나와 명암비 저하의 문제점이 발생하여, 이를 개선하기 위해 1 TV field에 한번의 리셋 방전을 사용하는 selective reset을 제안하였으나, flicker 현상이 동반되는 문제점이 발생하였다. [2]

본 연구에서는 기존파형을 selective reset 구동 시 발생하는 flicker 현상에 대한 원인을 살펴보고, 이를 제거할 수 있는 새로운 리셋 파형을 제안한다. 그리고 제안 된 리셋파형을 바탕으로 새로운 selective reset 파형과 실험결과를 보이겠다.

# 2. 본 론

## 2.1 실험 장치 및 방법

본 실험에는 3천국 면방전 반사형 구조의 7.5인치 패널이 사용되었다. 패널 내부의 가스 혼합비는 Ne-Xe(8%)이며, 내부압력은 500torr 이다. 각각의 셀은 사각격벽으로 분리되었으며, 서스테인 천국과 스캔 전국의 간격은 250tm의 장방전 구조이다. VDS로 제어하는 AWG(FTLab, HVA800)를 사용하여 구동파형을 설계하고, 패널에 적용하여 구동하였다. 파형과 방전 현상을 관찰하기 위해, 디지털 오실로스코프(Tektronix,TDS3054)와 광 측정기(Hamamatsu,C6385-01)를 사용하였다.

#### 2.2 장방전 구조의 새로운 리셋 파형 제안

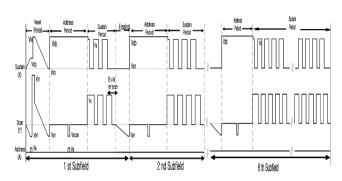

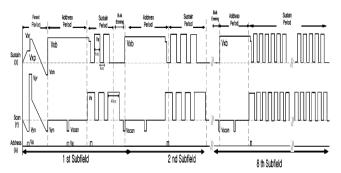

기존 파형으로 그림 1과 같이 8 subfield의 selective reset 을 구성하였을 경우, black광에서 flicker현상이 발생하였다. 이 flicker현상은 두 가지 원인으로 살펴볼 수 있다. 첫 번째는 서스테인 전압(Vs=270V)이 너무 높다는 점이다. 서스테인 전압이 보상하였으나, 서스테인 전압을 낮추고 8 subfield를 구동시키게 되면 flicker현상은 보이지 않았다. 이와 같은 특징으로 보아 서스테인 전압은 낮아져야 한다. 두 번째는 서스테인 전압을 낮춘 상태에서 1 TV field 기간동안한번의 리셋방전만 시켰을 경우, R,G,B 셀 중 green 셀에서만 방전이 깜박거리는 현상이 관찰 되었다. 이는 red와 blue 셀에서의 방전개시전압 보다 green셀에서의 방전하다 인당하게 발생하게 된다. 서스테인 전국에 형성된 음의 벽전하는 셀렉티브 리셋구동을 하지 않으면, 방전 공간안에 프라이밍 압자의 영향으로 안정적인 리셋방전이 가능하지만. 셀렉티브 리셋으로 구동하게 되면, 첫 번째 subfield에서 리셋 방전 후 7subfield의 시간이 흐른 후에 다시 리셋방

전을 하게 되므로, 방전공간에 프라이밍 입자가 부족하여, green 셀에서 flicker 가 발생되게 된다. 따라서 리셋기간동안 서스테인 전극에 형성된 음의 벽전하의 양을 줄여야한다. 그리고 첫 번째 subfield에서 서스테인 방전 후 두 번째 subfield의 Vxb전압 인가시 발생하는 X-A오방전을 없애기 위해 Vxb 전압을 낮추어야 한다. 하지만 Vxb 전압을 낮추게 되면, 어드레스 방전 후 서스테인 전극에 형성되는 음의 벽전하가 적은 양이 쌓이게 되며, 서스테인 방전에 영향을 끼쳐 불안정한 방전이 발생하게 된다.

〈그림 1〉 기존 파형의 selective reset 파형

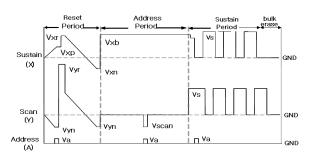

그림 2는 이 문제점을 해결하기 위해 새롭게 제안한 파형이다. 기존 파형에서 변화된 점은 리셋 기간동안 서스테인 전국의 종료 전위를 0V에서 ~Vxn(~130V)로 내려주었으며, peak 전압인 Vxr을 300V에서 220V로, 또한어드레스 기간동안 서스테인 전국에 인가되는 Vxb 전압은 기존 300V에서 220V로 낮추었다. 서스테인 전압은 기존 270V에서 250V로 낮추었으며, 서스테인 기간동안 안정적인 방전을 형성하기 위해 첫 번째 서스테인 방전이 발생할 때, 어드레스 전국에 Va 전압을 인가하였다. 그리고 각각의 표준 전압레벨은 Vyr = 480V, Vyn = -130V, Vscan = -120V, Vxp =100V 이다.

〈그림 2〉 제안된 새로운 리셋 파형

### 2.3 selective reset 파형 제안

제안된 리셋파형은 램프 펄스를 사용하지 않고 수직 펄스를 사용하여 3번의 강방전이 리셋구간에 발생하게 되어 백그라운드 광의 빛이 램프 펄스를 사용했을 때보다 많아지게 되고 이는 암실 명암비의 악화로 이어진다. 이를 개선하기위해 selective reset 파형의 개발이 필요하였다. 제안된 파형으로 그림 1과 같은 방식으로 구성하면, 서스테인 구간동안 스캔전국에 형성된 음의 벽전하는 bulk erase 구간에서 A-Y 방전을 일으켜 대부분의 양이 소거된다. 장방전 구조의 PDP를 방전시키기 위해선 서스테인 전국과 스캔전국사이에서 동시방전이 발생되지 않기 때문에 어드레스 전국을 트리거 전국으로서 이용하며, 또한 서스테인 전압이 높아지기 때문에 이 높은 서스테인 전압으로 인해 서스테인 방전을 통해 형성된 벽전압의 값이 크게 된다. 이 벽전압에 의해 방전이 발생되는

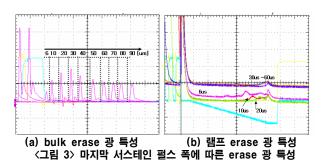

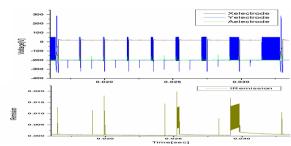

bulk erase를 통해 어드레스전극과 스캔 전극사이의 벽전하가 소거된 후, 이어 지는 램프 다운 erase구간에서 안정적인 어드레스 방전이 일어날 수 있도록 나 머지 초과되는 양을 소거한다. 기존 파형에서 나타났던 문제점인 X-A 오방전 과 black 광 flicker 현상은 제안된 리셋파형에서는 나타나지 않았기 때문에 셀 렉티브 리셋파형 설계시 가장 주안점을 두었던 점은 첫 번째 subfield에서 서스 테인 방전이 이루어진 후 다음 subfield들에서 어드레스 구간에서 발생된 어드 레스 전극과 스캔 전극사이의 오방전이다. 이 A-Y 오방전은 어드레스 방전이 일어나 서스테인 방전이 발생한 subfield에서 마지막 서스테인 방전을 통해 스 캔전극에 형성된 음의 벽전하가 서스테인 마지막 펄스에서 일어나는 bulk erase 구간과 램프다운 erase구간에서 충분히 지워지지 못하여, 다음 subfield의 어드 레스 구간에서 -120V의 스캔 전압이 인가될 때, data 신호가 인가되지 않아도, A-Y 오방전이 발생하는 것이다. 이 오방전 특징을 살펴보기 위해 그림 3과 같 이 스캔 전국에 인가된 마지막 서스테인 펄스 폭을 변화시켜 가면서, bulk erase 구간과 램프다운 erase 구간에서의 광세기를 비교하고 A-Y 오방전 양상 을 살펴보았다.

그림 3 (a)와 같이 벽전하에 의해 발생하는 A-Y bulk erase의 광세기는 스캔 전극 폭이 30us 까지는 증가하다가 30us 이후론 줄어들어 60us 이후 안정적인 광세기를 보인다. 서스테인 방전으로 발생한 프라이밍 입자와 더불어 펄스폭이 증가할수록 벽전하가 유전체에 안정적으로 쌓일 수 있기 때문에 30us까지는 강 한 bulk erase가 발생하여, 스캔 전극에 형성된 음의 벽전하를 줄여 주게 된다. 이는 그림 3 (b)의 램프 erase 구간에서 방전 개시 전압이 펄스폭이 증가할수 록 커지는 것으로 확인할 수 있다. 그림 3 (b)의 서스테인 펄스폭이 30us이상 이 되면 램프 종료 전위 근방에서 A-Y 방전이 미약하게 발생한다. 하지만, 10us와 50us의 서스테인 펄스폭에서 나타나는 bulk erase의 광세기가 거의 같 음에도 불구하고, 이후 램프 다운구간에서의 광세기에 차이가 나는 이유는 서스 테인 방전 후 유전체에 안정적으로 쌓이지 못하고 방전공간에 남아있던 벽전하 들이 펄스폭이 증가할수록 안정적으로 유전체에 쌓이기 때문이다. 어드레스 구 간에서 발생하는 A-Y 오방전은 서스테인 펄스폭이 30us이상이 되면 관찰되지 않았다.

여기서 주목할 점은 스캔 전극에 인가된 마지막 서스테인 펄스 폭이 30us이상인 경우 램프 erase 구간에서 방전이 발생하는 것 이 아닌 Vyn=-130V 까지 떨어진 종료 시점에서 미약하게 방 전이 발생하는 것을 알 수 있다. 이와 같은 방전 특성을 이용하 여 기존 램프 구간을 없애고 사각펄스를 이용한 파형을 고안 하 였다.

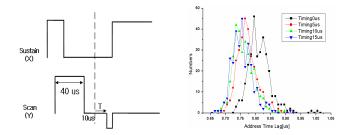

<그림 4> 마지막 서스테인 펄스폭에 따른 어드레스 지연시간

그림 4.는 마지막 서스테인 펄스폭을 결정하기 위해 진행한 실험이다. 펄스 폭 이 20us이상이 되면, 다음 서브필드의 어드레스 구간에서 A-Y 오방전이 발생 하지 않았으며, 펄스폭이 40us이상이 되면, 300회 샘플링하여 측정한 어드레스 지연시간 분포도가 일정해 지므로 펄스폭을 40us로 결정하였다.

그림 5.는 마지막 서스테인 펄스폭을 40us로 고정하고, 이후 사각펄스를 인가 하는 시점을 알아보기 위한 실험으로, 사각펄스를 10us이후 인가하면, 어드레스 지연시간 분포도가 일정해 지므로, 인가시점을 10us이후로 하였다.

(a) 인가 파형 개략도 (b) 어드레스 방전 지연시간 분포도 <그림 5> 40us펄스폭에서 시각 펄스 인가 시점에 대한 어드레스 지연시간

<그림 6> 제안된 selective reset waveform

그림 6은 이와 같은 결과를 바탕으로 제안된 selective reset 파형이다. 1 TV field(16.7ms)를 8서브필드로 분할하고 첫 번째 서브필드에서만 리셋을 시행하 며, 서스테인 구간에서 형성된 wall charge를 이후 서스필드의 어드레스 방전에 적합한 상태를 형성시켜 주기 위해 스캔 전극에 인가된 마지막 펄스를 40us 인 가하여 벌크 이레이지를 발생시키고, 이후 벽전하가 안정적으로 유전체에 쌓일 수 있도록 20us의 벽전하 축적기간을 둔뒤, Vscan=-120V의 사각펄스를 인가 하여, 어드레스 구간에서 오방전을 일으킬 수 있는 초과된 벽전하를 소거해 줌 으로써 안정적으로 어드레스 방전이 발생한다. 그리고 8서브필드의 스캔전극에 인가하는 마지막 펄스폭은 이후 첫 번째 서브필드의 리셋 방전을 통해 벽전하 를 제어 할 수 있으므로, 보통의 펄스폭(6us)을 인가한다.

<그림 7> 제안된 selective reset 파형의 어드레스 On/Off 특성

그림 7은 SF 2, SF 5, SF 7에서 어드레스 방전을 일으켰을 때 어드레스 방전이 일어난 서브필드에서만 서스테인 방전이 발생하였고, 어드레스 방전을 인가하지 않은 서브필드에서는 어떠한 오방전 없이 안정적으로 8서브필드가 동작하였다.

#### 3. 결 론

본 연구에서는 장방전 구조를 구동하기 위하여 기존 파형을 바탕으로 새로운 리셋 파형을 제안하고, 백그라운드 광을 줄일 수 있는 selective reset 파형을 고안하였다. 기존 방법으로 selective reset 시행 시 1TV field 중 1262us의 리 셋기간이 필요하나, 제안된 방법은 632us로 방전에 불필요한 이 기간을 반 이 상 줄여줌으로써, image quality향상에 도움을 줄 수 있으며, 1.55cd/m2의 블랙 휘도를 얻을 수 있었다.

# [참고문헌]

- [1] H. Kim, J. Y. Kim, and H. S. Tae, "New Long Gap Discharge mode Driven by Low Sustain Voltage for Highly Efficient plasma Displays," SID'04 Digest, pp510-513 (2004).

- [2] S. Kim, T.Y.Song, J. Y. Kim, S. H. Lee, J. H. Seo, and B. J.Shin, "Reset Waveform for Large-Sustain-Gap Structure in AC PDPs," IDW '06