# Novel AC bias compensation scheme in hydrogenated amorphous silicon TFT for AMOLED Displays

Kunjal Parikh\*, Kyuha Chung, Beomrak Choi, Joon-Chul Goh, Jong-moo Huh, Young-Rok Song, Namdeog Kim, Joonhoo Choi Samsung Electronics Co., LCD R&D Center, LCD Business, Kiheung, 449-900, Korea \*Phone: 82-31-209-6106, E-mail: kunjal.parikh@samsung.com

#### **Abstract**

Here we describe a novel driving scheme in the form of negative AC bias stress (NAC) to compensate shift in the threshold voltage for hydrogenated amorphous silicon (a-Si:H) thin film transistor (TFT) for AMOLED applications. This scheme preserves the threshold voltage shift of a-Si:H TFT for infinitely long duration of time(>30,000 hours) and thereby overall performance, without using any additional TFTs for compensation. We briefly describe about the possible driving schemes in order to implement for real time AMOLED applications. We attribute most of the results based on concept of plugging holes and electrons across the interface of the gate insulator in a controlled manner.

Keywords: amorphous silicon TFT, threshold voltage, AMOLED, bias stress, etc

## 1. Objectives and Background

AMOLED have gained considerable interest for flat panel displays due to their demonstrated capacity in high brightness, wide viewing angle, fast response times and lower manufacturing cost compared to LCD counterpart. Due to impressive performance attributes, AMOLED promises amongst most of the display manufactures to be sold at price points attractive to the mass consumer within a lucrative market segment of the display industry.

Low temperature poly-silicon (LTPS) is being widely used for the stable active matrix backplane. However LTPS has the limitation over the large area because of the limitation of excimer laser. It also suffers from very high production cost and non-uniformity over large areas<sup>1</sup>. There are several reports on non-laser techniques such as metal induced laser crystallization (MILC) in which crystallization is being favored by depositing metal layer over active surface and crystallizing the active channel area<sup>2</sup>. Also, lot of

work is being focused on Solid Phase Crystallization (SPC) in which crystallization is done using high temperature annealing<sup>3</sup>. However, even these techniques suffer from higher off current which determines the contrast ratio in the panel and have large non-uniformity. Henceforth, people have tried light-doped drain (LDD) technique to lower the off current which has higher the number of masks and have also applied expensive ion implantation method which amplifies the overhead cost of the production<sup>4</sup>. There have been couple of reports in which people have tried using optical<sup>5</sup> and electrical feedback system<sup>6</sup> to compensate the degradation of the TFT backplane and OLED. However, all the previous technologies rather increases the complexity of the AMOLED and thereby the cost of production.

Recently, hydrogenated amorphous silicon thin-film transistors (a-Si:H TFT) have been considered as the pixel elements of AMOLED due to their good uniformity and feasible fabrication processes for large-size and low cost panels<sup>7</sup>. However, a-Si:H, by virtue of its material structure, does not enjoy the same electronic properties, such as mobility, stability, etc as compared to above mentioned techniques. It is well-known that the stability of a-Si:H is rather poor with high threshold voltage shift due to electrical stress over time.

We, hereby report, negative bias AC stress which controls the shift in the threshold voltage properties of a-Si:H for very long duration of time (>30,000 hours). There are couples of reports in which people have tried using negative DC bias stress<sup>10</sup>, pulse bias stress<sup>11</sup>, and compensation circuits<sup>12</sup>. All the previous reports leads to effectively increase the threshold voltage shift (Vth) of a-Si:H TFT over the time. However, to the best of our knowledge this is the first AC bias stress scheme in which we can preserve the threshold shift characteristics for long duration of time (>30,000 hours) without using any additional TFT for compensation.

## 2. Experimental Procedures

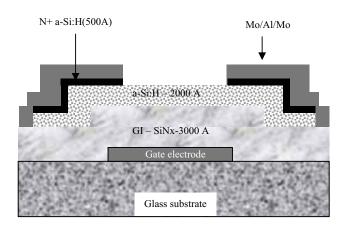

We have fabricated a-Si:H TFTs with channel dimension of (W/L) 200 x 4 μm with back channel etching structure. The cross section of the device is shown in fig. 1. After gate electrode patterning using Mo/Al/Mo, silicon nitride, undoped hydrogenated amorphous silicon and n+ doped amorphous silicon were deposited using plasma enhanced chemical vapor deposition (PECVD) without interrupting the process to maintain good interface quality between gate nitride and hydrogenated amorphous silicon. After n+/a-Si:H island patterning, the source drain metal were deposited by sputtering and etched away by wet etching.

Figure 1. The inverted staggered structure of a-Si:H TFT structure

The source-drain metal electrodes confine the channel region. N+/a-Si:H is etched away by dry plasma etching using SF6 and HCL gas mixture after source/drain patterning. In order to maintain good ohmic contact between source drain and active a-Si:H layer, highly doped n+ a-Si layer was used, and this layer captured the hole carrier effectively in the off-state, the details about which can be found elsewhere<sup>12</sup>.

#### 3. Results and discussions:

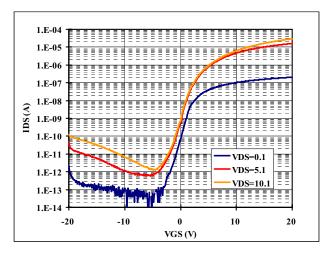

As shown in fig 2, the typical I-V transfer characteristics of in-house prepared a-Si:H is reported. The gate-source voltage is swept from -20 to +20 V with drain source voltage in the step from 0.1V to 10V to get the idea of the TFT from linear to

saturation region. All the TFTs reported from herein are produced in the same batch with the process variation of less than 5%. The mobility and Vth of the a-Si:H TFT reported here are 0.5 cm<sup>2</sup>/v-sec and 3V respectively.

Figure 2. Transfer I-V characteristics of in house prepared a-Si:H with SiNx as gate insulator.

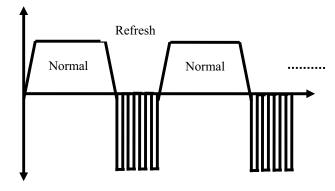

We applied the novel method of driving to these TFTs using negative AC bias stress as shown in fig. 3. We stress our TFT for 100 hours using the normal stress condition Vgs=7v and Vds=7V. This translates around  $3\mu A$  of current in our device which is sufficient enough to drive the OLED and peak white luminance. After 100 hours of stress, we refresh our TFT by applying negative AC bias stress at the frequency of 60Hz, voltage swing of 0/-20V for 25 hours. We continue this cycle of 4:1 duty ratio, 100 hours of stress and 25 hours of refresh, to repeat our results.

Figure 3. NAC showing the normal driving condition at Vgs=7V and Vds=7V for 100 hours and negative AC bias at 0/-20V, 50% duty cycle for 25 hours.

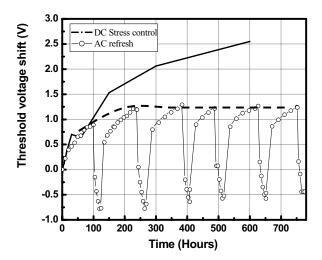

We adopted the refresh rate with the duty ratio of (4:1) and repeated the results for almost 800 hours. As seen from the Figure 4, we were able to control the Vth shift for prolonged amount of time without any further degradation (marked in dotted black line) compared to the control sample, without any refresh (marked in solid black line).

Figure 4. NAC of 0/-20 V, 60Hz, 50% duty cycle pulse after 100 hours of dc stress (in circles). Vth saturates on periodically applying NAR in 4:1 duty ratio as compared to constant DC stress (in solid)

To the best of our knowledge, AC refresh driving scheme is the first in the literature which can compensates the shift in the Vth for very high duration of time. We can readily implement this

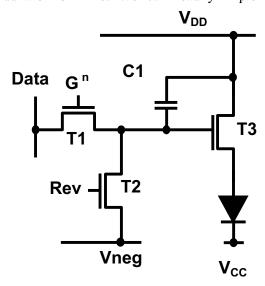

Figure 5. 3T circuit, extension of 2T circuit with capacitor. Extra T2 TFT can be used to implement NAC

scheme with widely used 3T driving pixel as shown in fig. 5. This 3T circuit is the extension of widely used 2T circuit for AMOLED devices. The extra T2 TFT can be used to apply the refresh to the driving TFT by simply changing the driving algorithm in the gate and data driver IC. Our research is underway to use this driving scheme for AMOLED displays.

We attribute our results based on plugging holes and electrons in a control fashion across the interface of gate insulator and active channel area. We do consider the influence of defect mechanism in the active silicon area over the time. However, much of the compensation is being attributed by refreshing the TFT pixel. We can progressively see the negative peak in the fig 4, shifting in the upward direction which indicates the defect mechanism developing over the time. However, our prolonged results for more than 800 hours indicates that this phenomena of defect mechanism is very small or rather not significant because of the higher quality of a-si:H active layer.

# 4. Impact

This work will have great impact in display area because of its unique quality of using in-house fabrication facilities without changing any materials, fabrication tools, any significant process architecture, etc. It will help the display industry to enjoy the merits of AMOLED display in terms of quality and cost compared to its counterpart AMLCD.

### 5. Acknowledgements

We would highly acknowledge all the engineers of OLED development team and fab workers in development line for the advancement of this work.

#### 6. References

- [1] Park et al, European Phys J, Appl. Phys. **31**, 3 (2005)

- [2] Kim et al, J. Korean Phys. Soc. 47, 404 (2005)

- [3] Choi et al, Amorphous and Nanocrystalline Silicon Sci. and Tech. **862**, 647 (2005)

- [4] Juang et al, Semiconductor Sci. Tech. **21**, 291 (2006)

- [5] Fish et al, SID Digest. 1120 (2004)

- [6] A. Nathan et al, SID Digest. 320 (2005)

- [7] J. J. Lie et al, SID Digest. 1516 (2003).

- [8] T. Tsumimura et al, SID Digest. 6 (2003)

- [9] T. Shirasaki et al, SID Digest. 1516 (2004)

- [10] Y. Tai Appl. Phys. Letts. 67, 76 (1995)

- [11] T. Tsujimura, Japanese J. of Appl. Phys. **43**, 5122 (2004)

- [12] J. H. Lee, J. H. Kim, M. K. Han, IEEE Electronics Device Letts. **26**, 12(2005)

- [13]Y. Chung et al, Japanese J. of App. Phys. **39**, 1051 (2000)