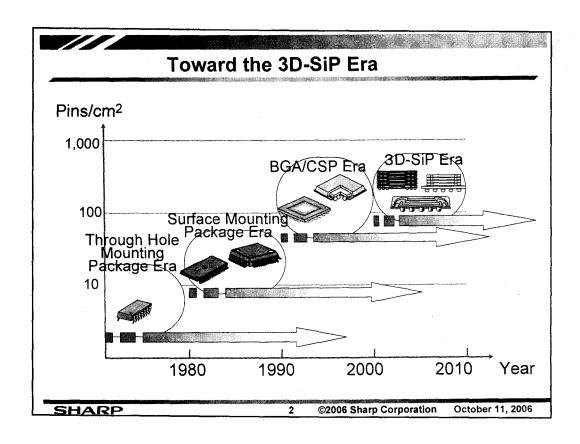

## Toward the 3D-SiP Era with New Technologies

Morihiro Kada

(Sharp/Japan)

The 5th International Symposium on Microelectronics and Packaging (ISMP 2006)

### **Toward the 3D-SiP Era** with New Technologies

Morihiro Kada Assembly and Packaging Development Dept. Sharp Corporation

SHARP

©2006 Sharp Corporation

# Chip stack and Package stack Stacked Die vs. PoP – Trade Offs Stacked Die PoP Prospects IDM ownership Smaller body size and lower package profile Prospects Tested at individual package level for Known Good Device

#### **Concerns**

- KGD required for high product yield

- Single-sourced product

- New development needed to change a device or handle die shrink

- Compound yield and multi test

#### Concerns

- Slightly larger / thicker Package stack

- Co-design for bottom and top packages

- · Infrastructure for package stacking

Source: Amkor Technology, Panasonic Factory Solutions, Senju Metal Industry, Sharp (ECTC2006)

SHARP

5

©2006 Sharp Corporation

October 11, 2006

# Chip Stacking Technology Pyramid Stacking Structure Normal Wire Bonding (Left) and Reverse Wire Bonding (Right) Chip on Wire (Cow) technology SHARP 6 ©2006 Sharp Corporation October 11, 2006

|                                           | Fan-out+Solder Ball Interconnect<br>(Sharp etc)                                    | Tape Substrate Interconnect<br>(A ) | ISM+ Wire Bond Interconnect (B) |                |

|-------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------|---------------------------------|----------------|

| Ownership                                 | Customer                                                                           | Logic Manufacture                   | Logic Manufacture               |                |

| Ex. Package<br>Top Memory<br>Bottom Logic | 14X14<br>0.5P(2S3R) 162max<br>0.5P(4S2R) 200max<br>0.5P 436max<br>(0.65P) (385max) | 13X11 0.65P 188<br>14X14 0.65P 336  | 14X14 13X13                     |                |

| Package Height (1Logic+2memory)           | 1.60max                                                                            | 1.55max                             |                                 |                |

| Production Line                           | Conventional +                                                                     | Conventional ++                     | Conventional ++                 |                |

| Die Shrink                                | 0                                                                                  | 0                                   | 0                               |                |

| Memory Testing                            | △<br>New Socket                                                                    | O<br>Current Testing System         | X<br>New C/K, New Socket        | O God<br>∆ Fai |

| Multi-layer Stacking                      | 0                                                                                  | Δ                                   | ×                               | X Poo          |

| Thermal performance                       | Δ                                                                                  | Δ                                   | Δ                               |                |

| Total Assessment                          | tal Assessment                                                                     |                                     | ×                               | 1              |

|    | PoP                                                                         |    | PiP                                                    |

|----|-----------------------------------------------------------------------------|----|--------------------------------------------------------|

| 1. | Uses solder ball (SMT infrastructure) to interconnect individual package.   | 1. | Uses wire bonding to interconnect individual package.  |

| 2. | Products are controlled by the customer.                                    | 2. | Products are controlled by the Logic manufacture.      |

| 3. | Diverse combinations are<br>available without additional<br>infrastructure. | 3. | Diverse combinations are available with additional ISM |

| 4. | Packages are usually larger in size.                                        | 4. | Packages are usually smalle in size.                   |

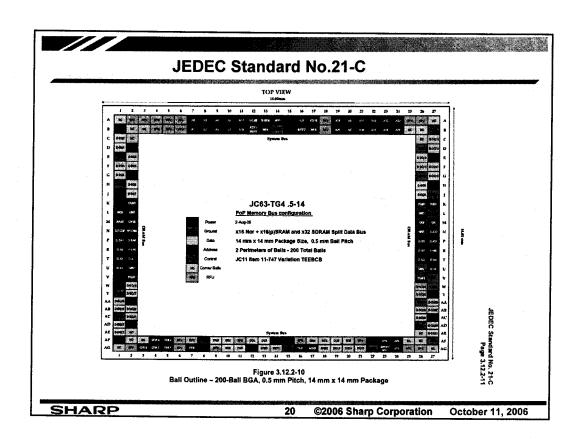

| Ī |     | Package                                                                                     | Memory Bus Supported                                                                                                                                                                                                                         |

|---|-----|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ī | 1   | 11 mm x11 mm Package 0.65<br>mm Ball Pitch<br>2 Perimeters of Balls -<br>112 Total Balls    | x16 Nor +x16(p)SRAM<br>+x16 SDRAM<br>+x16 NAND<br>shared databus                                                                                                                                                                             |

|   | 2   | 12 mm x12 mm Package 0.65<br>mm Ball Pitch<br>2 Perimeters of Balls -<br>128 Total Balls    | x16 Nor +x16(p)SRAM<br>+ x16 SDRAM<br>+ x16 NANDshared databus                                                                                                                                                                               |

|   | 3 . | 15.00 mm x15 mm Package<br>0.65 mm Ball Pitch<br>2 Perimeters of Balls -<br>160 Total Balls | Options                                                                                                                                                                                                                                      |

|   | 4   | 16.00 mm x16 mm Package<br>0.65 mm Ball Pitch<br>2 Perimeters of Balls -<br>176 Total Balls | Options                                                                                                                                                                                                                                      |

|   | 5   | 14 mm ×14 mm Package<br>0.5 mm Ball Pitch<br>2 Perimeters of Balls -<br>200 Total Balls     | x16 Nor +x16(p)SRAM<br>and x32 SDRAM<br>Split Data Bus                                                                                                                                                                                       |

|   | 6   | 14mm x14mm Package<br>0.65mm Ball Pitch<br>21 x21 Ball Matrix<br>152 FBGA                   | Options                                                                                                                                                                                                                                      |

|   | 7   | 13mm x13mm Package<br>0.65mm Ball Pitch<br>19 x19 Ball Matrix<br>136 FBGA                   | Options Bus A Bus B Bus C  AA x32 (Lower 16 bits) x32 (Upper 16 bits) x16 NAND  M-DRAM + NOR M-DRAM + NOR  AB x32 (Lower 16 bits) x32 (Upper 16 bits) NOR x16 NAND  NOR + pSRAM + pSRAM + pSRAM  AC x16 M-DRAM x16 ADQ NOR(A24 Max) x16 NAND |

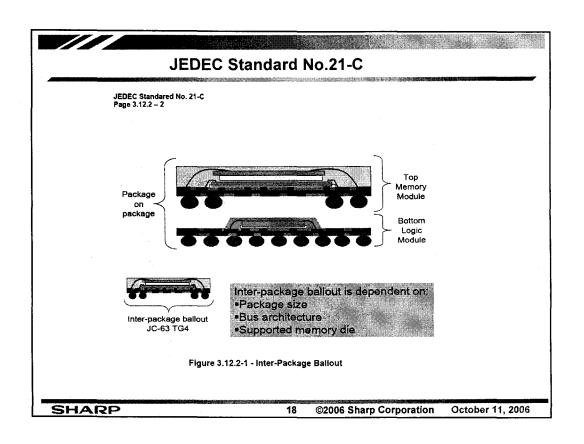

#### **JEDEC PUBLICATIONS 95 Design Guide 4.22**

**JEDEC DESIGN STANDARD**

DESIGN REQUIREMENTS FOR OUTLINES OF SOLID STATE AND RELATED PRODUCTS

#### **JEDEC PUBLICATION 95**

Design Guide 4.22

Fine-pitch, Square Ball Grid Array Package (FBGA) Package-on-Package (PoP)

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

Date: November 2008

Issue: A

A CONTRACTOR OF THE CONTRACTOR

SHARP

21 ©2006 Sharp Corporation

October 11, 2006

#### **Current and Future Issues in PoP**

- Full-fledged use of PoP only have just begun, many issues still remain, such as

- -Device supply

- -Expansion of standardization

- -Stacking infrastructure improvement

- There are also fundamental issues:

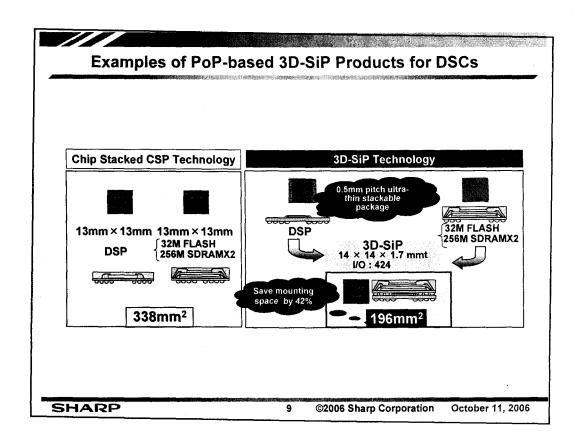

- -Current PoP packages are stacked with a fan-out structure, package size is larger than in chip stacking,

- -The top package is often memory, for which a chip stack package is used, while a single chip is used for the bottom package to keep package height low.

SHARP

22 ©2006 Sharp Corporation

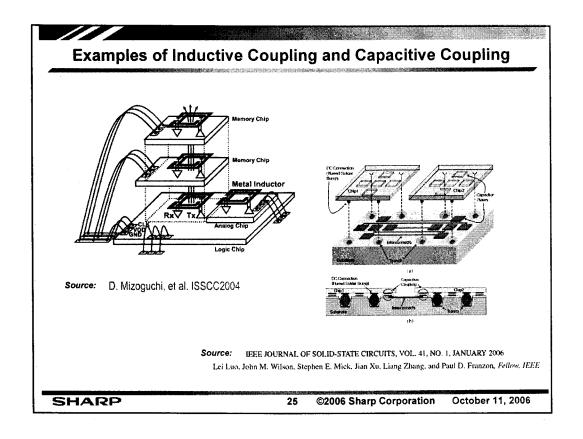

#### **New Stack Interconnect Technology**

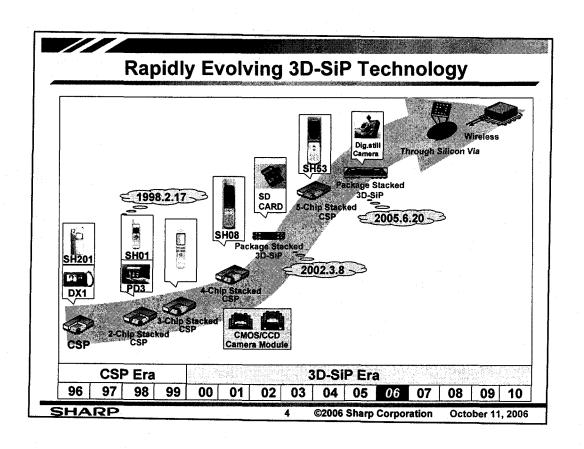

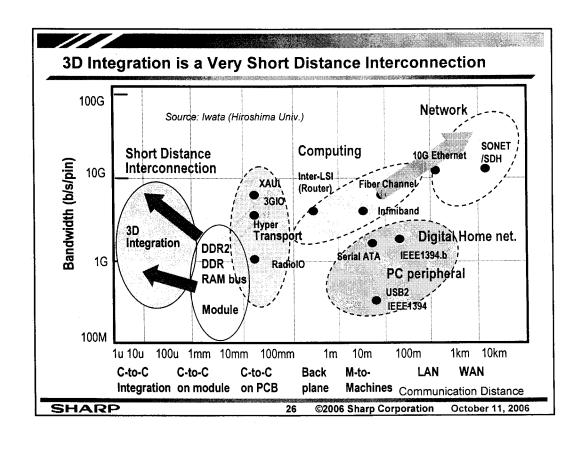

Chip and package stacking have already been adopted commercially and are core technologies in 3D-SiP,but new technologies are starting to gain attention. These can be divided into the following three categories:

- 1. Through-Silicon Via Technology

- -Chip on Chip

- -Chip on Wafer

- -Wafer on Wafer

- 2. Wireless Interconnect Technology

- -Inductive Coupling

- -Capacitive Coupling

- -Electromagnetic Wave Coupling

- 3. Optical Interconnect Technology

SHARP 23 ©2006 Sharp Corporation October 11, 2006

#### **Categories of New Interconnect Technologies** Monolithic Interchip **Board Level Interconnect** Multilayer Metal **Bonding Wire** PCB Transmission Line Wired Through Si Via Cable: coaxial cable, Flat Interconnect Transmission Line Inductive (L) Coupling Short Distance Wireless Capacitive (C) Coupling Very Short Distance interconnect Electromagnetic Coupling (Antenna) Long Distance Optical Integrated Optical Device Optical Circuit Board Interconnect Planar waveguide Optical Fiber Source: Iwata (Hiroshima Univ.) SHARP 24 ©2006 Sharp Corporation October 11, 2006

#### **Characteristics of New Interconnect Technologies**

|          | Interconnect Technology<br>(Distance) | Data Rate              | Power<br>Consumption | Interconnect<br>Density | Process | Cost | Chip Testing |

|----------|---------------------------------------|------------------------|----------------------|-------------------------|---------|------|--------------|

| Wire     | Bonding Wire                          | X (2Gbps)              | х                    | Х                       | Δ       | Δ    | Δ            |

|          | Through Si Via                        | lwata (Hiro<br>(8Gbps) | shima Univ           | ersity)                 | N<br>X  | X    | Δ            |

| Wireless | Inductive Coupling                    | O(10Gbps)              | 0                    | Δ                       | Ō       | 0    | 0.8          |

Source: Iwata (Hiroshima Univ.)

SHARP

27 ©2006 Sharp Corporation

October 11, 2006

#### Conclusion

- 1. In the near future, these technologies will contribute new types of 3D-SiP.

- 2. However, whether TSV or some other technology will become dominant, and which technologies will be used in which applications depends on the results of R&D yet to come.

- 3. It is hoped that when these new technologies become the mainstream, they will produce 3D-SiPs that surpass SoC and usher in a new generation in the semiconductor industry.

SHARP

28 ©2006 Sharp Corporation