# Recent Trend in Japanese Packaging Technology

Sei-ichi Denda

IMAPS-Japan

2nd Korea-Japan Advanced Semiconductor Packaging Technology Seminar

## Recent Trend of Japanese Packaging Technology

October 26, 2000 in Seoul

IMAPS Japan Nagano Institute of Technology **Dr.S.Denda**

## Technological Topics under Development and in Pre-Production

- ·Various Wafer Level Packaging

- ·Chip Stacked High Density Devices

- ·Thin Package with Paper Thin Chips

- ·Extension of Flip Chip Interconnection

- ·Pb Free Soldering Adoption Roadmap

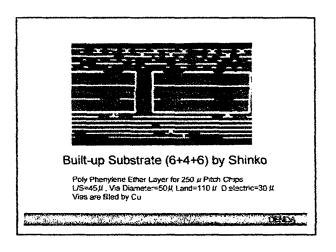

- ·Higher Density Built-up Substrate

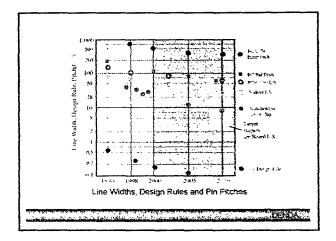

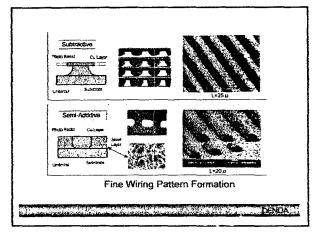

- -Finer Wring Pattern for Redistribution

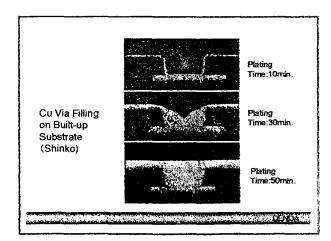

- ·Cu Plating Via Filling Mechanisms

- · Substrate Materials Development

CENTA

### Next Generation Technology Development in Institutions

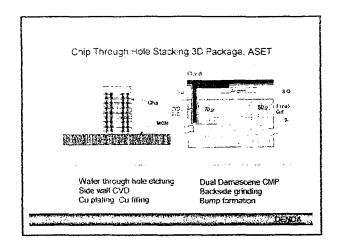

- -3D Chip Stacking with Chip Through Hole

- Optoelectronic Packaging

- Active Research Groups at Universities, Tokyo-U,

Waseda-U, Shinshu-U, Okayama-U, Osaka-U

- Japan Institute of Electronics Packaging (JIEP-IMAPS Japan)

- •Pb Free Soldering Development (NEDO-EiAJ-

- -Super Connent Program (10 µ range technology)

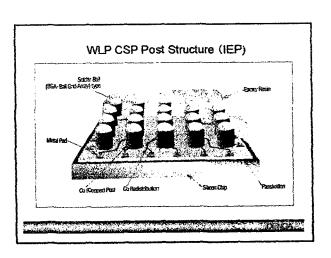

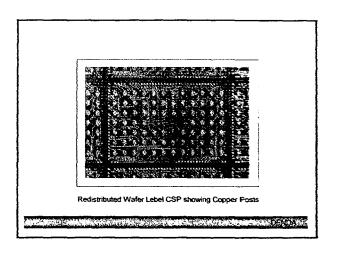

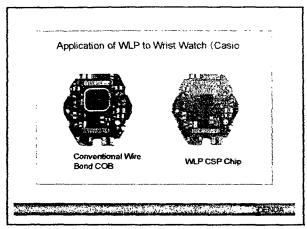

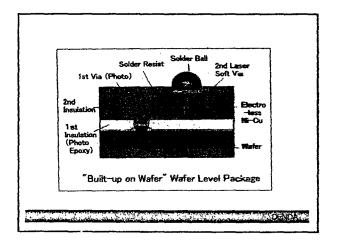

### Wafer Level Packaging- WLP

- •WLP is aiming at lower device cost than CSP

- Redistribution is essential for penpheral pad chips

- -Reliability is assured by resin coating

- ·Redistributed flip chip is WLP group

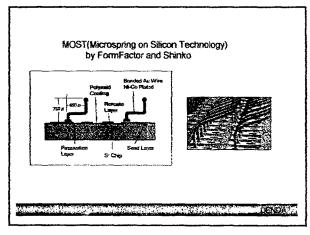

- -MOST is growing

- ·New WLP company started

- ·Bumping business started

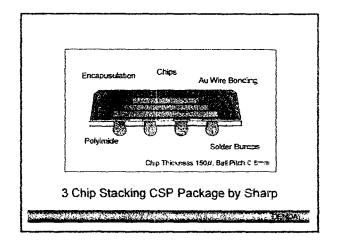

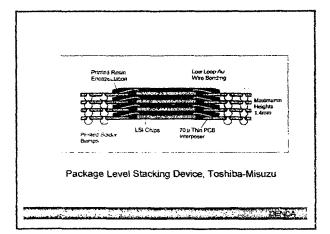

## Chip Level Stacking Device Mainly for Cellular phone Needed more memories -2-3 chip CSP by wire bonding or flip chip Low loop wire bonding -Thickness is limited, 1.4mm -Chips are ground to 50 µ -Sharp, Toshiba, Fujitsu, Rohm, Epson -ASET approach is chip through hole

# Package Level Stacking Device ·40-50 μ thick chips are packaged ·Device can be tested before stacking ·Dicing Before Grinding technology ·Grinding after packaging -Au or solder bumps ·Total heights less than 150 μ ·Toshiba, NEC, Misuzu. Atomnics, Shinko, Ibiden

### Flip Chip Interconnection

- •Bump pitch close to 150  $\mu$  (area), 60  $\mu$  (SBB)

- Microprocessor with C4 bumps and built-up substrate

- -ACF and NCP connection and underfill

- ·SSB becoming more popular

### High Performance BGA

- •Enhanced BGA with high speed signal and better thermal characteristics

- -Double Layer tape interposer

- ·Metal heat spreader

- 800-1000 pins

A CONTRACTOR OF THE CONTRACTOR