# Balanced Comparator and Delta-Sigma Modulator with High-T<sub>c</sub> Multilayer RSFQ Logic Circuits

## 고온초전도 다층박막 RSFQ 회로를 이용한 균형잡힌 비교기와 델타-시그마 모듈레이터

Yonuk Chong, Z. G. Khim, B. Ruck\*, R. Dittmann\*, C. Horstmann\*, A. Engelhardt\*, G. Wahl\*, B. Oelze\*, and E. Sodtke\*

정연욱, 김정구, B. Ruck\*, R. Dittmann\*, C. Horstmann\*, A. Engelhardt\*, G. Wahl\*, B. Oelze\*, and E. Sodtke\*

Department of Physics, Seoul National University, Seoul 151-742, Korea \*Institut für Schicht- und Ionentechnik, Forschungszentrum Jülich, D-52425 Jülich, Germany

서울특별시 관악구 신림동 서울대학교 자연과학대학 물리학과 \*Institut für Schicht- und Ionentechnik, Forschungszentrum Jülich, D-52425 Jülich, Germany

We demonstrate small-scale high-T<sub>c</sub> superconductor RSFQ(Rapid Single Flux Quantum) circuits using multilayer bicrystal technology. An RSFQ balanced comparator is demonstrated with good current resolution, and its operating conditions are discussed in some detail. A single-loop delta-sigma modulator is realized adding a feedback loop to the comparator. The effect of the feedback is confirmed by dc measurement and simulation. A design of an RSFQ toggle flip-flop with the same multilayer bicrystal technology is suggested.

#### 1. Introduction

Rapid single flux quantum(RSFQ) logic has been suggested as competitive candidate for a low power ultra-fast superconducting electronics [1]. Various circuits have been developed with low- $T_c$  superconductors, and several small-scale circuits have been recently demonstrated with high- $T_c$  superconductor.

The ground plane is essential for small inductances required for proper RSFQ circuit operation with large critical current junctions. Since high-T<sub>c</sub> multilayer Josephson junction technology is still premature, we adopted bicrystal junctions in multilayer thin films to

demonstrate high- $T_c$  RSFQ circuits with ground plane[2]. Here we report a successful fabrication and operation of a balanced comparator and delta-sigma modulator.

## 2. Balanced Comparator

#### 2-1. Fundamentals

The balanced comparator is the basic RSFQ component, which consists of two series -connected Josephson junctions[3]. It compares the input current with some reference value, and gives a single flux quantum(SFQ) voltage pulse output at the clock frequency when the

input is greater than the reference. Since RSFQ logic enables very fast sampling rate up to several hundred GHz, high dynamic response is possible. When the comparator receives a SFQ pulse, one of the two junctions should change Exactly which junction to its phase by 2π. switch is determined by the additional input current into the central node of the comparator. The reference current level can be adjusted by adding a constant offset current to the current Depending on whether the current input. input is higher or lower than the reference level, every incoming sampling pulse will switch either the upper(J3) or the lower(J4) junction, and leave the state of the other Output SFQ pulses are junction unchanged. generated only when the lower switches.

(b)

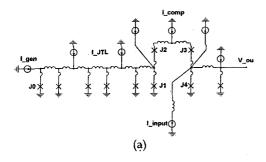

Figure 1 (a) the circuit diagram of the balanced comparator (b) operation of the balanced comparator at 57K with  $V_g = 120 \, \mu V_g$ , or 60 GHz equivalently.

## 2-2. Design and Operation

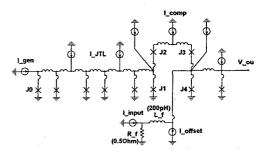

Figure 1(a) shows the circuit diagram of the fabricated balanced comparator. It consists of a generator junction(J0), Josephson transmission line(JTL), SFQ buffer(J1,J2) and the comparator (J3,J4). The JTL is biased by a single current source through PdAu on-chip resistors. This is just the part of the delta-sigma modulator explained in the next section.

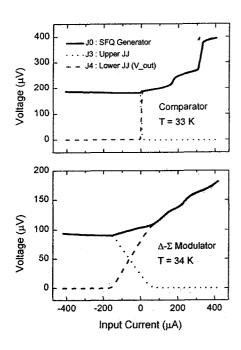

Operation of the comparator is shown in the figures 1(b). The generator junction was biased at a constant voltage state and generates sampling SFQ pulses with a frequency proportional to the bias voltage. The SFQ pulses are put into the balanced comparator through the JTL and the buffer stage.

As we increase the input current, the output changes from zero to voltage abruptly generator voltage (sampling frequency divided Josephson characteristic 483MHz/µV). As we increase the input current further, the output voltage ceases to follow the voltage, at which point comparator cannot sustain the high pulse rate. We measured the comparator operation up to 73 K, however, obviously it would work at higher temperatures than 77 K.

## 2-3. Current Resolution

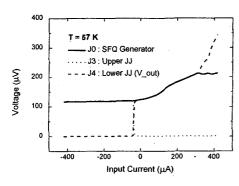

As we see in figure, the transition is not perfectly abrupt near input~reference, where each of the junction has a finite probability of The effective transition width (current resolution) AI of this gray zone affects essentially on the sensitivity of the SFQ analog-to-digital converters(ADC's), and also reduces the parameter margins. It is known that  $\Delta I$  depends on several factors such as the speed of the driving pulse train, the effective output impedance of the driver, the energy scale of the thermal and quantum fluctuations, etc. Therefore, it is important to find a proper working point with the smallest AI. It is also known that this current resolution is dependent

Figure 2 The change of the current resolution according to the bias current I\_comp at 68K with  $V_g = 50 \mu V$ .

on the bias current on the comparator loop(I\_comp). Figure 2 shows the change in the effective width for different bias current at 68 K with  $V_g = 50 \mu V$ . As we change the bias current resolution changes current, the periodically as shown in the figure. This period of the working point is also dependent on temperature. As temperature increases, the period decreases. This can be understood if we take the total inductance of the comparator loop(J1-J4) into account. Since the kinetic inductance increases steeply in the temperature range of interest, the inductance per square also increases. Hence we need less current in putting a flux quantum into the loop.

## 3. Delta-Sigma Modulator

## 3-1. Fundamentals

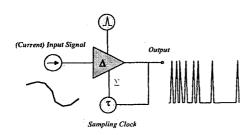

By adding a feedback loop to the comparator, a single loop superconducting

delta-sigma( $\Delta$ - $\Sigma$ ) modulator was implemented. The delta-sigma modulation is a technique for increasing the S/N ratio by oversampling and feedback. The basic principle of this technique is that the feedback re-shapes the spectrum of the quantization noise, pushing most of the noise power to high frequencies, well outside the signal band, and then out-of-band signal is by the digital filter. removed conventional AD/DA converters require high -accuracy analog components in order to achieve high overall resolution, the delta-sigma modulation can trade resolution in time for resolution in amplitude in such a way that imprecise analog circuits may be used.

RSFQ has the unique advantage that very fast sampling rate is possible. This enables large oversampling ratio, which is essential in high-resolution high-speed AD/DA converters. Noise shaping in low- $T_c$  superconducting  $\Delta$ - $\Sigma$  modulators has been already demonstrated using niobium technology[4]. High- $T_c$  superconductor results were also presented recently by the same group[5].

The essential difference between the usual PCM(Pulse Code Modulation) and sigma-delta ADCs was described in the excellent review by Candy and Temes[6]. Sigma-delta uses an integrator to continuously sum the sampled analog signal (the  $\Sigma$  operation). This integrated signal is converted to a digital word. A feedback mechanism subtracts this quantity from the total integrated signal (the  $\Delta$  operation).

Quantization of a signal introduces inevitable quantization error  $e < \pm 1/2$  LSB, and this can be treated as noise. The oversampling ratio(OSR), defined as the ratio of the sampling frequency  $f_s$  to the Nyquist rate  $2f_o$ , is given by the number

$$OSR = f_s/2f_o$$

It is well known that simple oversampling reduces the in-band rms quantization noise n by the square root or the oversampling ratio,

that is,

$$n = e/\sqrt{OSR}$$

The signal to noise and distortion(SINAD) is defined as the rms of the fundamental divided by the sum of all spectral components in the passband excluding the dc component. The effective resolution N is then given by

$$SINAD = (6.02N + 1.76) dB$$

Therefore, each doubling of the sampling frequency decreases the in-band noise by 3 dB, increasing the resolution by only 0.5 bit.

In case of the first-order delta-sigma modulation, the feedback reduces the noise at low frequencies by re-shaping the originally uniform spectral noise density as

$$N(f) \propto (1/\sqrt{f_s}) \sin(w/2f_s)$$

If the sampling frequency is much higher than the signal band, the noise power that falls into the signal band is,

$$n \propto e/(OSR)^{3/2}$$

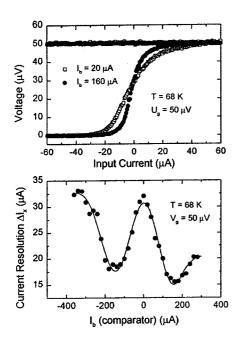

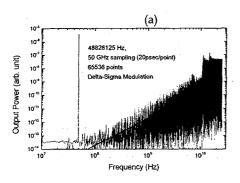

Figure 3 (a) basic principle of the delta-sigma modulator (b) simulation result of the noise-shaping by the modulation

(b)

Therefore, each doubling of the oversampling ratio thus reduces this noise by 9 dB and provides 1.5 bits of extra resolution.

Since the delta-sigma modulator does not require precise component for quantization, this fits itself well into the relatively less mature superconducting technology. Figure 3 shows the basic principle and the simulation result for a single loop delta-sigma modulator. In this simulation, the power spectrum of the PCM-encoded modulator output is obtained by For calculation, fast Fourier transform(FFT). 65536 sampled points were taken, and 50 GHz sampling is assumed, corresponding to picoseconds between each sampled point. pure sinusoidal signal of 48.8 MHz is used for input(OSR=50). Noise shaping by the feedback

(b)

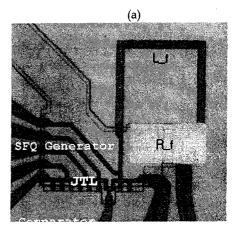

Figure 4 (a) circuit diagram of the single-loop delta-sigma modulator (b) photograph of the fabricated circuit

is clearly seen in the figure. The above-calculated noise spectral density is drawn together for comparison.

## 3-2. Design

Figure 4 shows the circuit diagram of our single-loop delta-sigma modulator the photograph of the fabricated circuit. The comparator itself is just the same as what we described in the previous chapter. RL circuit serves as integrator that consists of a long superconducting strip line inductance (200pH) and a PdAu on-chip resistor(0.5Q). The L/R time constant should be considerably larger than the sampling intervals. pulse decreases the input current exactly by the amount of  $\Phi_o/L_{feedback}$  , indicating advantage of the RSFQ as an analog quantity with the quantum mechanical accuracy.

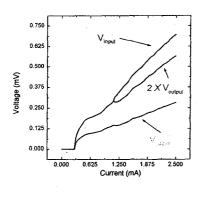

Figure 5 Characteristics of the balanced comparator and the  $\Delta$ -Σ modulator. The widening of the transition width is the indication of the feedback operation.

## 3-3. Measurement

To confirm the noise shaping, high-speed measurement is required. But our measuring probe was designed only for dc measurement, hence it has the bandwidth of a few kHz at most. But the effect of the feedback loop can be clearly seen in the dc measurement, as shown in the figure 5. The major change in current-voltage characteristic is broadening of the effective transition width  $\Delta I$ . The output is linear within the transition region, and the slope is independent of the bias current into the comparator. This simply reflects the fact that the delta-sigma modulation doesn't depend strongly the detailed on characteristic of the comparator.

To check the linear response of the modulator, we measured the output signal from a pure sinusoidal input of 19360 Hz. The result is shown in figure 6. The ratio of the signal and the first harmonic was 40 dB, or 5-6 effective bits equivalently[7]. It is still far from useful, but we believe that the noise floor is determined by the measurement setup, and the

actual resolution is better.

## 4. Design of a T Flip-flop

The multilayer bicrystal technology can be readily applied to demonstrate small-scale Josephson devices with ground plane. Since the high-T<sub>c</sub> Josephson technology is primitive, the bicrystal junctions can be used as the first step to prove the possibility of high-T<sub>c</sub> The right strategy we Josephson devices. should take might be that we now test several layouts and circuit design with the currently available bicrystal junctions and multilayer, and wait for a breakthrough in the high-Tc When high quality Josephson technology. Josephson junctions become available, then the

Figure 7 (a) Design of a T flip-flop with multilayer bicrystal Josephson junctions. (b) Simulation or IV characteristics with optimum circuit parameters

(b)

knowledge learned by the bicrystal circuits becomes quite useful.

As another application of the multilayer bicrystal Josephson junction technology, a toggle flip-flop (TFF) is designed. Figure 7 shows the layout and simulation result with optimum circuit parameters. Here, the 3-dimensional structure provides flexibility to the single-line bicrystal substrate. A 3-dimensional structure has already suggested using Nb junctions (named as "stacktron")[8], and this will help increasing packing density of the superconducting circuits.

## References

[1] K. K. Likharev and V. K. Semenov, IEEE Trans. Appl. Supercond. 1, 3 (1991).

[2] Y. Chong, B. Ruck, R. Dittmann, C. Horstmann, A. Engelhardt, G. Wahl, B. Oelze, and E. Sodtke, Appl. Phys. Lett. **72**, 1513 (1998).

[3] B. Oelze, B. Ruck, E. Sodtke, A. F. Kirichenko, M. Yu. Kupriyanov and W. Prusseit, Appl. Phys. Lett. 70, 658 (1997).

[4] J. X. Przybysz, D. L. Miller, E. H. Naviasky, and J. H. Kang, IEEE Trans. Appl. Supercond. 3, 2732 (1993).

[5] M. G. Forrester, B. D. Hunt, D. L. Miller, J. Talvacchio, and R. M. Young, ISEC '99 Extended Abstract, pp29-31.

[6] J. C. Candy and G. C. Temes, "Oversampling Delat-Sigma Data Converters Theory, Design, and Simulation", IEEE Press, 1992.

[7] Other peaks observed in the output spectrum were confirmed to arise from various instruments in the lab. This implies indirectly that the high frequency shielding is not so good in our measurement setup.

[8] B. Ruck, R. Schmitz, N. Thyssen, B. Hermanns, H. Kohlstedt, S. Lomatch, ASC '98, to appear in IEEE Trans. Appl. Supercond.